Новое вычисляемое заранее управление генерирует те же управляющие сигналы, что и FSD, но машина теперь имеет очень регулярную структуру: управляющие сигналы поступающие из регистра R.k€ out (k - 1) управляют этапом kпутей данных для всех k > 1. Действительно, если мы определим R.0 и R.1 как фиктивные регистры длиной 0, то же самое потребуется для всех k. Структура путей данных и вычисляемого заранее управления машины DLXσ иллюстрируются рисунком 4.10.

Аппаратная часть, генерирующая входы регистра R.2 является автоматом Мура с 10 состояниями EX, вычисляемыми заранее управляющими сигналы и параметрами exиз таблицы 4.10. Состояние noEXслужит начальным состоянием автомата. Следующее состояние зависит только от входа IRно не от текущего состояния. Включая регистры R.3 и R.4, управляющие сигналы этапов EX - WB могут быть вычислены заранее со следующей стоимостью и временем цикла:

CCON(moore) = СpMoore(ех) + (3 + 2) * Cff TCON(moore) = TpMoore(ex).

Сигналы Mealy, которые управляют этапом ID, генерируются автоматом Mealy с одним состоянием и параметрами idиз таблицы 4.10. Все его входы обеспечиваются регистром IR с нулевой задержкой. Согласно разделу 2.6, стоимость этого автомата и задержка сигналов Mealy может быть представлена как

CCON (mealy) = CMealy(id) + (3 + 2) * Cff

ACON (mealy) = Ao(id).

Мы не будем утруждать себя анализом стоимости и временем цикла механизма останова.

4.2.4 Основное наблюдение

Позже мы установим правильность конвейерной машины показав, что она моделирует машину DLXσ . Это требует индуктивного доказательства на основе такт за тактом. Мы всегда будем говорить о фиксированной но произвольной последовательности

I = I0, I1, ...

команд, которой предшествует сброс и которая сама не прерывается сбросом.

Если в течении такта сигнал busyактивен, тогда состояние машины не изменяется до конца этого цикла. Следовательно, мы перечислим только циклы в течении которых сигнал busy неактивен

T = 0,1,...

Для таких циклов Т и сигналов Rмы обозначим через RTзначение Rв течении цикла T; Rтакже может быть выходом регистра. Мы вводим сокращение

![]()

означающее, что команда Ii находится на этапе kмашины DLXσв течении цикла T. Формально это может быть определено как

• выполнение начинается в цикле T = 0, т.е., Iσ(0,0) = 0,

• если Iσ(k,T) = iи k < 4, тогда Iσ(k + 1, T + 1) = i,

• если Iσ(4,T) = i, тогда Iσ(0, T + 1) = i + 1.

Для любых других комбинаций Tи kфункция планирования Iσ(k,T) не определена. Следовательно,

Iσ(k,T) = i <-> T = 5*i + k <-> i=[T/5] и k = T mod 5;

и для любого цикла Т >= 0, этап kполон (fullT[k] = 1) тогда и только тогда, когда Iσ(k, T) определено. Повторимся, что мы обозначаем через Ri значение Rпосле выполнения команды Ii. Через R-1мы обозначаем начальное значение R, т.е., значение Rпосле сброса. Основное наблюдение о работе такт за тактом машины DLXσ формулируется в следующей лемме.

|

Лемма 4.3 |

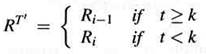

Dateline Лемма. Пусть I(k, T ' ) = i ипусть R € out(t), тогда

Это проиллюстрировано на рисунке 4.11. В течении цикла T', регистры выше этапа kуже имеют новое значение Ri, тогда как регистры ниже этапа kвсе еще имеют старое значение Ri-1. Другими словами, на нисходящих стрелках рисунка 4.3 машины DLXσ, читаются значения Ri из текущей команды, тогда как на восходящих стрелках машиной читаются значение Ri-1 из предыдущей команды.

Очень интуитивная формулировка леммы – причина, по которой на рисунке 4.3 мы перенесли файл регистров общего назначения в самый низ конвейера а не – как обычно – в середину этапа ID. Формальное доказательство использует тот факт, что

Ri-1 =R5i

и выполняется для T = 5i + kиндукцией по k. Мы оставляем простые подробности на упражнение 4.2.

Другой, очень интуитивный способ осветить это лемму - следующий. Вообразите, что провода между этапами конвейера настолько длинны, что мы можем обернуть

|

|

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.