где Dmri, является сигналом чтения памяти данных для Ii. Вместе с сигналом записи GPRwфайла регистров и некоторыми другими вычисляемыми заранее управляющими сигналами, сигналы v[4 : 2] конвейеризируются в регистрах R.2, R3 и R.4 как показано на рисунке 4.15. Для любого этапа k € {2,3,4}, сигналы GPRw.kи v[k].kдоступны на этапе k. В конце этапа kтакже доступны следующие сигналы C'.k:

• C'. 2, который является входом регистра MAR,

• С'.3, который является входом регистра C,

• C'.4, который является данными, записываемыми в файл регистров GPR.

Видно, что сигналы C' .kявляются входами выходных регистров этапа k. Поэтому в определенных циклах к этим сигналам можно применить первую часть теоремы. Это является критичным для корректного доказательства логики пересылки. Очевидно, верны следующие утверждения:

|

Лемма 4.8 |

Для всех i, для любого этапа k>=2, и для любого цикла Т при Ia(k, T) = i утверждаем:

1. Ii переписывает регистр GPR[r] только после последовательного выполнения Ii, адрес r, отличный от 0, содержится в регистрах Cad.k и сигналы записи GPRw.k - включены, т.е.:

|

Ii пишет GPR[r] /\ v[k]i = 1 <-> C'.kT = GPR[r]t. |

Ii пишет GPR[r] <-> (Cad.ki) = r /\ r =/= 0 /\ GPRw.ki = 1.

2. Если Ii пишет регистр GPR[r] и если после ее последовательного выполнения флаг правильности v[k] является включенным, тогда значение сигнала C' .k в течении цикла Т равно значению записанному Ii, т.е.:

Кроме того, C' .k синхронизируется в выходной регистр этапа k в конце цикла T.

|

|

Рисунок 4.15 Структура путей данных DP и вычисляемого заранее управления CON расширенной DLXπмашины

На этапе декодирования сигналы правильности получаются из сигнала чтения памяти Dmr, который вычисляется заранее управляющим автоматом. Поэтому генерация и буферизация сигналов правильности требует следующих стоимости и времени цикла:

СVALID = (3 + 2 + 1) • Cff + Qinv

TVALID = Tauto + Dinv .

Это расширение улучшает стоимость и время цикла вычисляемого заранее управления в конвейерной конструкции DLX.

4.4.2 3-х этапная пересылка

Мы опишем схему Forwспособную пересылать данные из трех этапов j = 2,3,4 в этап 1. Она имеет следующие входы

1. Cad.j, C'.j, GPRw.jкак описано выше,

2. адрес adсогласованный с Cad,

3. данные Dinиз порта выходных данных файла регистров,

и она имеет выход Doutподающий данные на этап 1. Данные Dinпередаются на этап 1 всякий раз, когда отправление невозможно.

|

|

Рисунок 4.16 Блок-схема цепи Forw(3) и механизма пересылки

Пути данных конвейерной машины DLXπдополнены механизмом пересылки, состоящим из двух схем Forw(3), как изображено на рисунке 4.16. Одна из схем передает данные в регистр A, другая передает данные в регистр B. В общем, механизм пересылки будет заботится о всей транспортировке данных из высших этапов к низшим, за исключением адрес памяти команд. Таким образом, в верхнеуровневых схемных решениях путей данных (рисунок 4.17) больше не будет восходящих граней между этапами 1 - 4.

Мы переходим к определению схемы Forw(3), дадим простейшую реализацию и затем докажем теорему 4.7.

Схема Forw

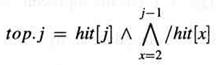

Для этапов j € {2,3,4}, мы определим следующие сигналы:

hit[j] = (full.j /\ GPRw.j) /\ (ad =/= 0) /\ (ad = Cad.j).

Сигнал hit[j], как предполагается, показывает, что регистр, к которому производится обращение командой на этапе 1, изменяется командой на этапе j. За исключением первых четырех циклов синхронизации Т = 0,... 3 все конвейерные этапы полны (таблица 4.13), т.е., они обрабатывают регулярные команды. Однако, в течение начальных циклов пустой этап предотвращен от сигнализирования установкой его флага заполнености. Сигнал

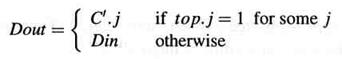

кроме того, показывает, что там не происходит установка на этапах выше этапа j. Тогда выход данных Doutвыбирается как

|

|

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.