Таблица 4.14 Иллюстрация функции планирования Iπдля этапов 1 - 4.

|

этап s |

Iπ(s, T) Iπ(s,T-1) |

|

1 |

i |

|

2 |

i-1 |

|

3 |

i-2 |

|

4 |

i-3 i-4 |

4. k = 1 (декодирование). В любой конструкции, этап декодирования имеет входные регистры IR€ out(0) и GPR€ out (4). Покажем, что IRTπ = IRT'как и выше. Если команда Ii не читает регистр GPR[r] при r =/= 0, мы сможем это сделать, поскольку выходы этапа 4 не используются. В других случаях, может быть использовано только значение GPR[r]T. Функция управления подразумевает (таблица 4. 14)

Iπ(4,T-i) = i-4.

Для i >= 4, мы заключаем, используя лемму 4.3 при s = 4, что

GPR[r]Tπ = GPR[r]i-4по индукционной гипотезе

.= GPR[r]T 'σ .

Согласно гипотезе теоремы, команды Ii-3 - Ii-1 не пишут в регистр GPR[r]. Следовательно

GPR[r]i-1 = GPR[r]i-4.

i <= 3. Обновление файла регистров GPR разрешается сигналом ue[4]. Поэтому механизм останова (таблица 4.11) гарантирует, что файл регистров не обновится в течении циклов t€ { 1 , 2, 3} . Таким образом,

GPR-1 = GPR]1π= ... = GPR4π.

Гипотеза теоремы подразумевает, что команды Ijпри 0 <= j < 3 не пишут в регистр GPR[r]. Следовательно,

|

QED |

GPR[r]-1 = ... = GPR[r]i-1.

По лемме 4.3 при s = 4 мы заключаем

GPR[r]4П = GPR[r]i-1 = GPR[r]aT '.

Аргумент полностью как и прежде.

4.3.2 Аппаратная стоимость и время цикла

В дальнейшем мы определим стоимость и время цикла конструкции DLXπ. За исключением окружения PC и механизма останова, конвейерная конструкция DLXπи подготовленная последовательная конструкция DLXσодинаковы. Так как в разделе 4.2 окружения конструкции DLXσописаны подробно, мы можем сфокусироваться на окружении PC и механизме останова.

Окружение PC

PCenv (рисунок 4.12) управляется теми же самыми управляющими сигналами что и конструкция DLXσ , glue logic PCglueтакже остается той же самой. Единственное изменение в PCenv является то, что отвергнут регистр DPCзадержанного PC. Память команд IMтеперь адресуется

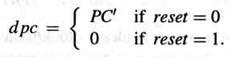

Однако окружение PC все еще принадлежит механизму отсроченного PC, где dpcтребует размещения DPC.

Из-за изменения окружение PC становится дешевле на один 32-битный регистр. Новая стоимость

CPCenv = 2*Сff(32) + 4*Сmux(32)+Сadd(32)+Сinc(30) + СPCglue.

Время цикла TPCenvокружения PC остается неизменным, но адрес dpcпамяти команд теперь имеет большую задержку. Принимая, что сигнал resetимеет нулевую задержку, адрес является верным при

APCenv(dpc) = Dmux(32).

Эта задержка складывается с временем цикла этапа IF и с накопленной задержкой сигнала ibusyпамяти команд:

tif = APCenv(dpc) + DIMenv(IR} + ΔAIMenv(ibusy) = APCenv(dpc) + dIstat.

Механизм останова

определяет для каждого этапа iсигнал разрешения обновления ue[i] согласно рисунку 4.13. Регистры full[4 : 2] синхронизируются CEкогда ни память команд, ни память данных не заняты или в течении reset :

CE = /busy \/ (reset /\ / ibusy) = /busy \/ (/reset NOR ibusy) /busy = ibusy NOR dbusy.

В течении сброса обновление задерживается, пока не закончится выборка команды. Так как сигнал resetимеет нулевую задержку, синхронизирующий CEможет быть сгенерирован с накопленной задержкой

Astall(CE) = max {AIMenv (ibusy), ADMenv (dbusy)} + Dnor + Dor.

Для каждого регистра R€ out(i) и памяти M € out(i), механизм останова комбинирует сигнал запроса синхронизации/записи и сигнал обновления и превращает их в сигнал синхронизации/записи:

Rce' = Rce /\ ue[i], Mw' = Mw /\ ue[i].

Обновление памяти данных DM разрешается, только если этап 3 полон и нет сброса:

Dmw' = Dmw /\ full[3] /\ ![]() .

.

Управляющий автомат Мура обеспечивает 7 сигналов запроса синхронизации/записи и сигнал Dmw' (таблица 4.9). Вместе с двумя вентилями AND для синхронизации этапов IF и ID, механизм останова имеет стоимость

Сstall = 3 • Cff + 4 • Cand + Qinv + 2 • Cnor + Cor + (7 + 2 + 2) • Cand .

Как и в последовательной конструкции, синхронизация регистра добавляет задержку Dff + δ, тогда как обновление файла регистров добавляет задержку Dram3(32,32) + δ. Таким образом, механизм останова требует время цикла

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.