Рисунок 4.11 Иллюстрация леммы 4.3. В текущем цикле Ii на этапе k.

машину вокруг экватора (так, что этап kбудет восточней этапа k + 1 mod 5). Теперь вообразите, что мы выполняем одну команду в день и что мы синхронизируем этапы конвейера с dateline, т.е., границей между сегодня и вчера. Тогда лемма заявляет, что к востоку от dateline мы уже имеем сегодняшние данные, а к западу от dateline мы все еще имеем вчерашние.

Пусть I(4, T) = i, тогда I(0, Т + 1) = i+ 1, и dateline лемма применима для всех R

RT+1 = R(i+1)-1 = Ri.

4.3 Конвейеризация как трансформация

Двумя очень простыми изменениями мы трансформируем подготовленную последовательную машину DLXσиз предыдущего раздела в конвейерную машину DLXπ :

1. Регистр DPC, т.е., задержанный PC, отвергнут. Память команд IMтеперь напрямую адресуется PC'. При сбросе, память команд адресуется по адресу 0 и PC' инициализируется значением 4. Это показано на рисунке 4.12. Регистр PC' все еще синхронизируется

PCce \/ reset.

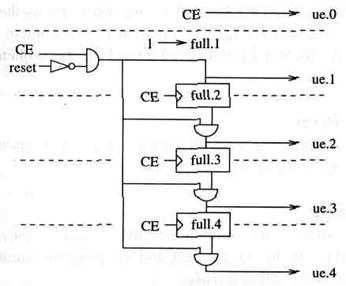

2. Используется механизм останова на рисунке 4.13. Для всех i, сигнал ue разрешает обновление регистров и ячеек RAM в out(i). Обновление памяти данных DM разрешается теперь

full3 /\![]() .

.

|

|

Рисунок 4.12 Окружение PC конструкции DLXπ , осуществляющее задержку PC

Рисунок 4.13 Механизм останова DLXπ

При сбросе, сигналы ue[4 : 0] инициализируются 00001. Когда подсчитываются только такты Т с неактивным сигналом busy, сигналы разрешения обновления ueстановятся активными в последовательности, показанной в таблице 4.11. Обратите внимание, мы теперь принимаем, что сигнал сброса будет активным в течении цикла Т = 0.

4.3.1 Корректность

Мы хотим показать, что согласно некоторым гипотезам конвейерная машина DLXπмоделирует подготовленную последовательную машину DLXσ . Мы должны

Таблица 4.11 Активация сигналов разрешения обновления ue[4 : 0] после сброса

|

т |

reset |

ue[0] |

ue[l] |

ue[2] |

ue[3] |

ue[4] |

full[2] |

full[3] |

full[4] |

|

0 |

1 |

1 |

0 |

0 |

0 |

0 |

* |

* |

* |

|

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

2 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

|

3 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

|

4 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

... |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

рассуждать одновременно о регистрах Rвстречающихся в машине DLXπи их аналоге в машине DLXσ . Поэтому, мы вводим запись Rπдля обозначения регистра в машине DLXπ ; мы обозначаем через Rσсоответствующий регистр в машине DLXσ. Запись Ri (содержимое регистра Rв конце команды Ii) будет использоваться только для последовательной машины DLXσ.

Длительность сброса

Мы предполагаем, что сигнал сброса активен достаточно долго, для того, чтобы разрешить доступ к памяти команд.

Начальные состояния

Регистры видимые программисту – универсальные регистры GPR, ячейки RAM в IM и DMи программные счетчики. Остальные регистры называются невидимыми.

Предположим, что в течении сброса моделирующая машина (здесь DLXσ) и моделируемая машина (здесь DLXπ) имеют одинаковое содержимое памяти и файла регистров. При последовательном выполнении сброс дается в цикле T' = -1 тогда как при конвейерном выполнении сброс дается в цикле Т = 0. Конструктивно обе машины не обновляют регистры общего назначения и ячейки памяти в течение сброса. Таким образом, в двух конструкциях DLX любой регистр R€ {GPR, PC', DPC} и любая ячейка памяти M из DMи IMдолжны удовлетворять

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.