Министерство образования и науки РФ

Новосибирский Государственный Технический Университет

Кафедра ВТ

Курсовой проект по дисциплине

«Моделирование»

Факультет: АВТ

Группа: АМ-215

Студент: Белоглазов А. В.

Преподаватель: Шалагинов А. В.

Новосибирск, 2005 г.

1. Постановка задачи. 3

2. Условное графическое обозначение моделируемого узла. 3

3. Назначения выводов узла. 3

4. Режимы работы узла. 4

5. Реальные задержки распространения сигналов микросхемы. 4

6. Описание работы узла. 5

7. Моделирование узла в пакете DesignLab 8. 5

7.1. Условное графическое изображение проектируемого узла в виде иерархического символа. 5

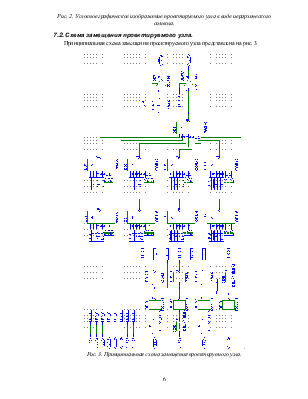

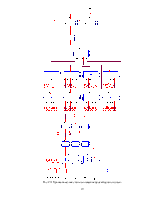

7.2. Схема замещения проектируемого узла. 6

7.3. Текстовое SPICE-описание моделируемого узла. 7

7.4. Содержимое файла описания внешних воздействий. 8

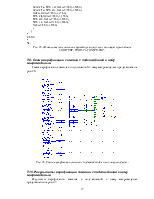

7.5. Схема верификации иерархического символа. 10

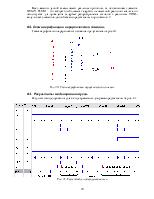

7.6. Результаты моделирования узла. 10

7.7. Оценка предельных скоростных возможностей исследуемого узла. 14

7.8. Функциональное описание проектируемого узла. 15

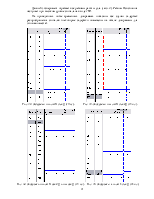

7.9. Схема верификации символа с подключённой к нему макромоделью. 17

7.10. Результаты верификации символа с подключённой к нему макромоделью. 17

8. Моделирование узла в пакете OrCAD 9.1. 18

8.1. Иерархический символ проектируемого узла. 18

8.2. Схема замещения проектируемого узла. 18

8.3. Схема верификации иерархического символа. 20

8.4. Результаты моделирования узла. 20

8.5. Поведенческая VHDL-модель узла. 23

8.6. Схема верификации узла с подключённой VHDL-моделью. 25

8.7. Результаты верификации поведенческой VHDL-модели узла. 25

9. Моделирование узла в пакете Active HDL 6.1. 26

9.1. Макромодель, представленная как иерархический символ. 26

9.2. Схема верификации иерархического блока, поддерживаемого схемой замещения. 28

9.3. Результаты верификации иерархического символа со схемой замещения. 28

9.4. Поведенческая модель узла на языке VHDL. 30

9.5. Схема верификации иерархического блока, поддерживаемого поведенческой VHDL-моделью. 31

9.6. Результаты верификации иерархического блока, поддерживаемого поведенческой VHDL-моделью. 32

10. Выводы. 33

10.1. Выводы по результатам работы. 33

10.2. Сравнительный анализ использованных в работе пакетов и личные впечатления. 33

11. Список использованной литературы. 34

Приложения. 35

Приложение 1. Макромодели элементов схемы. 35

Приложение 2. VHDL-модели элементов схемы. 38

Создать структурные и поведенческие модели цифрового узла в пакетах DesignLab 8, OrCAD 9.1, Active HDL 6.1. Провести имитационные эксперименты с разработанным узлом. Целью экспериментов является подтверждение работоспособности узла и соответствие его временных задержек требуемым.

Произвести сравнительный анализ использованных инструментальных средств проектирования и сделать личные впечатления о них.

Исследуемый цифровой узел: КП15 — мультиплексор 8-1 с выводом разрешения выходных данных, с прямым и инверсным выходами с третьим состоянием. В качестве конкретного экземпляра взята микросхема КР1533КП15, зарубежный аналог — SN74ALS251.

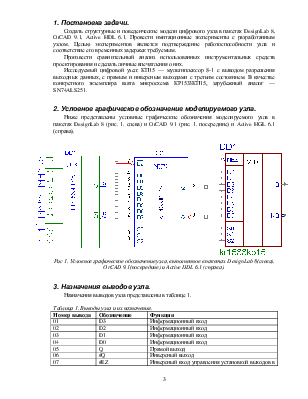

Ниже представлены условные графические обозначения моделируемого узла в пакетах DesignLab 8 (рис. 1. слева) и OrCAD 9.1 (рис. 1. посередине) и Active HGL 6.1 (справа).

|

|

|

|

Рис 1. Условное графическое обозначение узла, выполненное в пакетах DesignLab 8(слева), OrCAD 9.1(посередине) и Active HDL 6.1 (справа).

Назначения выводов узла представлены в таблице 1.

Таблица 1. Выводы узла и их назначения.

|

Номер вывода |

Обозначение |

Функция |

|

01 |

D3 |

Информационный вход |

|

02 |

D2 |

Информационный вход |

|

03 |

D1 |

Информационный вход |

|

04 |

D0 |

Информационный вход |

|

05 |

Q |

Прямой выход |

|

06 |

#Q |

Инверсный выход |

|

07 |

#EZ |

Инверсный вход управления установкой выходов в третье состояние |

|

09 |

S2 |

Вход выбора |

|

10 |

S1 |

Вход выбора |

|

11 |

S0 |

Вход выбора |

|

12 |

D7 |

Информационный вход |

|

13 |

D6 |

Информационный вход |

|

14 |

D5 |

Информационный вход |

|

15 |

D4 |

Информационный вход |

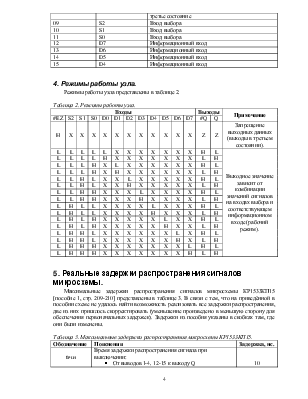

Режимы работы узла представлены в таблице 2.

Таблица 2. Режимы работы узла.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.