Программа выполнения лабораторной работы 4

в САПР XilinxISE 6.2 и

Active-HDL 7.1

Цель работы – физическая реализация проекта в ПЛИС XC9572XL-TQ100 и отладка его на учебном стенде SDK 7.1:

· Изучить дополнительные требования, предъявляемые к проекту для загрузки его в реальную микросхему CPLD XC9572XL с учётом ограничений отладочного стенда SDK 7.1.

· Познакомиться с архитектурой и характеристиками CPLD XC9572XL.

· Разработать и добавить в проект модели необходимых отладочных компонентов (инверторов, мультиплексоров, счётчиков-делителей частоты, преобразователей двоичного кода для управления семисегментными индикаторами и т.п.);

· Закрепить порты проекта за конкретными выводами ПЛИС с помощью интерактивного графического редактора PACE (Pinout and Area Constraint Editor);

· создать конфигурационную последовательность (JED - файл) для разработанного проекта;

· Загрузить проект в микросхему XC9572XL с архитектурой CPLD, пользуясь услугами программатора iMPACT, и выполнить его отладку на учебном стенде SDK7.1.

Перед началом работы запустите интегрированную среду проектирования Active-HDL 7.1, откройте в ней своё рабочее пространство и создайте новый проект Lab4.

ЗАДАНИЕ 1. Изучение учебно-практического стенда SDK7.1. Внесение в ранее созданный проект дополнительных отладочных элементов.

Ориентировочное время выполнения задания – 60 мин. (2 балла).

1.1. Познакомьтесь с описанием учебно-практического стенда SDK 7.1. Оцените его ресурсы, выясните, какие дополнительные отладочные модули вам понадобятся. Разберитесь с компонентами принципиальной схемы SDK 7.1.

1.2. Перенесите (или скопируйте) в проект Lab4 VHDL – описание ранее созданного и верифицированного цифрового автомата, например файл count5_hde.vhd – двоичный суммирующий счётчик по модулю 5.

1.3. Разработайте и протестируйте VHDL - модели дополнительных отладочных элементов, которые вам понадобятся при отладке проекта на стенде (инверторы, мультиплексоры, преобразователи двоичного кода в семисегментный, счетчик-делитель частоты). Не забывайте про инструменты LanguageAssistant(языковый помощник) и IPCOREGenerator (генератор VHDL-кода стандартных цифровых объектов).

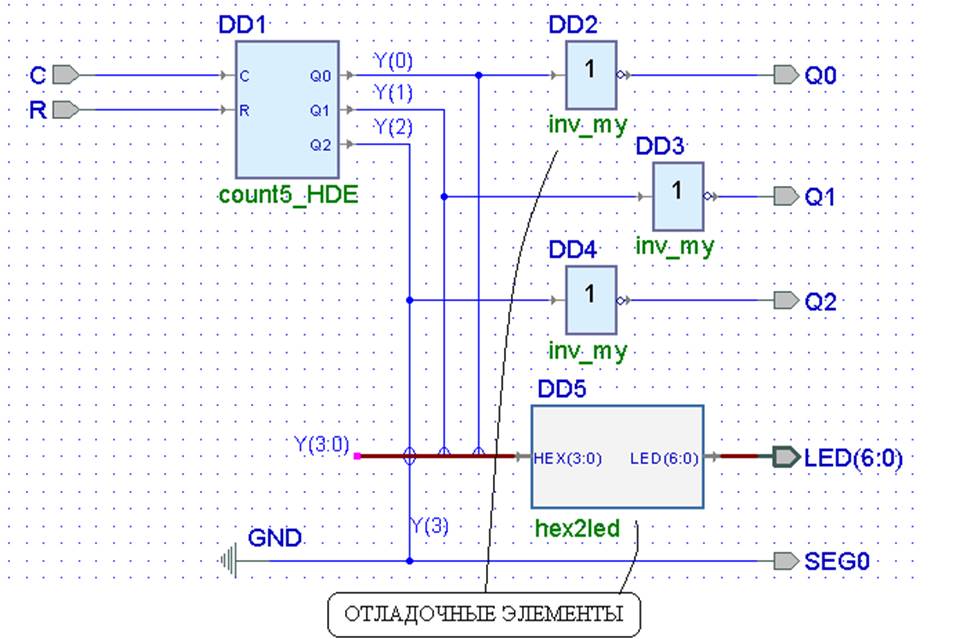

1.4. Создайте схемное описание модуля верхнего уровня,

например test_count5_hde. bde,

содержащего ваш проект в виде VHDL – модели (первый вариант решения) и дополнительные

отладочные элементы (рис.1). Не забудьте добавить в него выходные порты SEG0

и/или SEG1. Подключите их к земле (команда PowerSymbol из меню Diagram или пиктограмма ![]() ).

).

Рис.1. Схема проекта верхнего уровня с дополнительными отладочными элементами

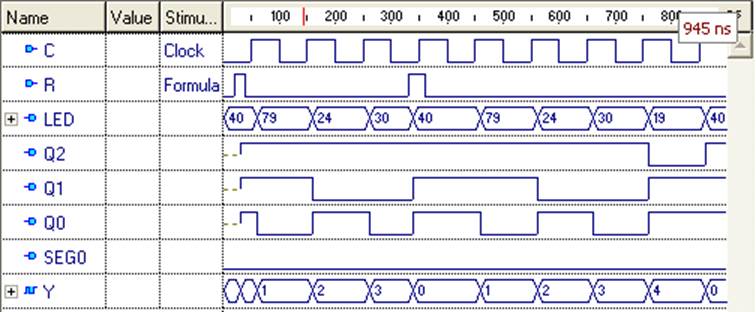

1.5. Выполните функциональное моделирование модифицированного проекта. Сохраните результаты моделирования в волновом файле, например test_count5_hde.awf(рис.2).

Рис.2. Тестирование проекта, подготовленного для испытательного стенда

SDK 7.1 (с дополнительными отладочными элементами)

ЗАДАНИЕ 2. Закрепить порты проекта за конкретными выводами ПЛИС с помощью интерактивного графического редактора PACE (Pinout and Area Constraint Editor).

Ориентировочное время выполнения задания – 45 минут (1 балл).

2.1. Передайте проект на синтез и реализацию в САПР Xilinx ISE 6.2. Не забудьте в настройках указать имя только что промоделированного проекта верхнего уровня. Убедитесь, что XilinxISE 6.2 открыл нужный проект.

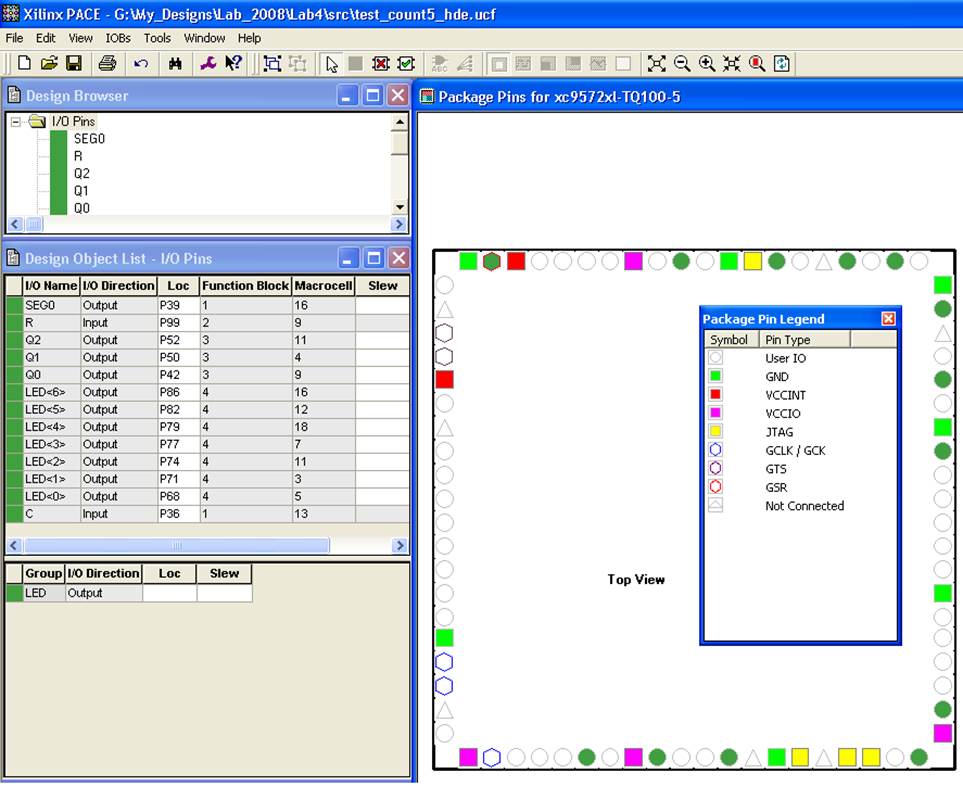

2.2. Выделите в окне SourcesinProject имя синтезируемого проекта, и запустите в окне ProcessesforSources процедуру AssignPackagePins (назначение контактов).

Дождитесь, пока программа выполнит всю предварительную работу: синтез и трансляцию проекта. После этого автоматически запустится интерактивный графический редактор PACE.

2.3. В окне Design Object List I/O Pins вы увидите полный список всех портов вашего проекта. В левом столбце перечисляются их имена, в следующем – указывается направление передачи сигнала (вход или выход), третий столбец LOC пустой. Именно в этом столбце надо указать номера контактов ПЛИС, к которым система должна подключить порты вашего проекта. Номер контакта задаётся в формате P<номер контакта микросхемы>.

Например, вы хотите, чтобы сбросом управлял двухпозиционный переключатель SW7 (см. описание стенда SDK 7.1). На принципиальной схеме стенда видно, что этот переключатель соединён с выводом ПЛИС, имеющим номер 36. Следовательно, напротив имени порта R (от слова RESET) надо ввести текст P36.

Если вы пожелаете, чтобы младший разряд выходного кода в вашем проекте Q0 управлял светодиодом D6, который на стенде подключён к выводу ПЛИС с номером 42, то в третьем столбце списка напротив имени порта Q0 надо напечатать P42.

Аналогичным образом устанавливается соответствие между номерами контактов и компонентами стенда для всех остальных портов вашего проекта (рис.3). Эта процедура носит название «назначение контактов» (AssignPackagePins).

2.4. Сохраните созданный список. Он будет записан в файл, имя которого совпадает с названием вашего проекта, а расширение файл получит *.UCF (от User Constraint File). Файл будет сохранён в папке synthesis вашего проекта, и при новом запуске САПР Xilinx ISE будет потерян.

Чтобы избежать отрицательных эмоций, лучше поступить иначе. Вернитесь к пункту 1.1 и вновь выделите в окне SourcesinProject имя синтезируемого проекта и щёлкните на нём правой кнопкой мыши. В открывшемся меню исполните команду New Source.

На экране монитора появится диалоговая панель с тем же названием. В левом окне выберите строку ImplementationConstraintsFile, введите имя файла, например test_count5_hde и укажите место его расположения, например, в папке src (от слова source).

Рис.3. Графический интерфейс программы PACE

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.