Содержимое этой папки не перезаписывается, так что UCF-файл не будет теряться. Однако не стоит забывать, что при внесении изменений в проект, он может перестать соответствовать действительности (например, при изменении числа портов или их имён).

Сохранив UCF-файл, откройте его ещё раз, но теперь уже в текстовом редакторе и убедитесь, что в нём всё правильно. С этой целью достаточно активизировать процесс EditConstraints (Text).

ЗАДАНИЕ 3. Создание файла конфигурации, загрузка его в ПЛИС и отладка физически реализованного проекта на учебном стенде SDK 7.1. Ориентировочное время выполнения задания – 45 мин. (1,0 балл).

3.1. Выделите в окне SourcesinProject строку с названием вашего проекта и запустите процесс GenerateProgrammingFile. Если процесс завершится без ошибок, то в папке synthesis вашего проекта должен появиться файл конфигурации в формате JEDEC, имеющий расширение *.JED. Убедитесь, что он там есть. Сохраните данный файл на внешнем носителе и скопируйте его в папку Configure_files на рабочий компьютер преподавателя, к которому подключён учебно-практический стенд SDK 7.1.

3.2. Запустите программатор iMPACT в автономном режиме (из стартового меню или щёлкнув по иконке, показанной ниже).

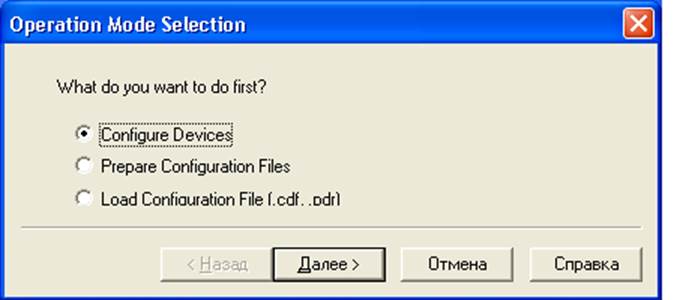

Откроется диалоговая панель программы iMPACT, которая выполнит все необходимые действия по загрузке проекта в микросхему. На первой панели (рис.4) вам надо выбрать режим ConfigureDevices (он предлагается по умолчанию).

Рис.4. Выбираем режим конфигурирования устройства

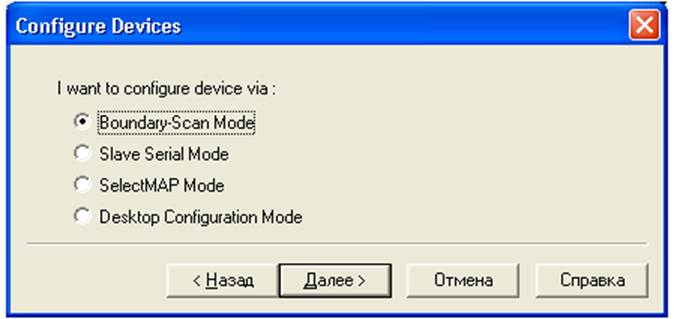

На второй панели (рис.5) вам будет предложено указать способ конфигурирования микросхемы. По умолчанию установлен режим Boundary-ScanMode – конфигурирование через JTAG-интерфейс. Именно этот режим используется для стенда SDK 7.1. Поэтому и здесь оставляем всё, как есть.

Рис.5. Указываем способ конфигурирования – Boundary-Scan Mode

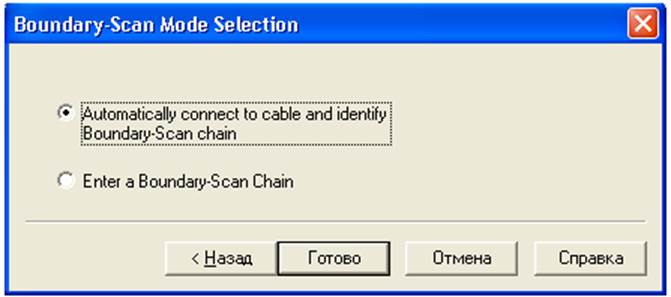

Затем система предложит автоматически выполнить подключение загрузочного кабеля и определить JTAG-цепочку: AutomaticallyconnecttocableandidentifyBoundary-Scanchain. Здесь тоже не стоит экспериментировать (рис.6).

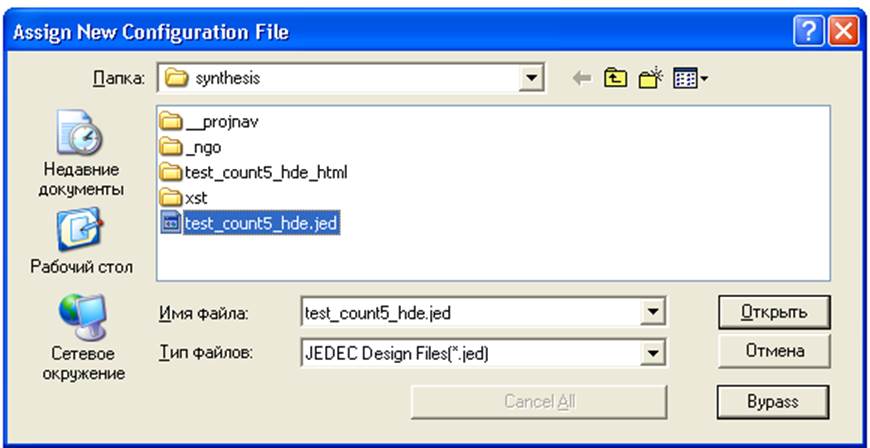

После инициализации JTAG-цепочки автоматически откроется диалоговая панель для выбора файла конфигурации (рис.7). Укажите нужный файл (вы уже знаете, что он имеет расширение *.JED) и приступайте к программированию микросхемы.

Рис.6. И здесь соглашаемся с установками по умолчанию

Рис.7. Выбираем желаемый файл конфигурации микросхемы

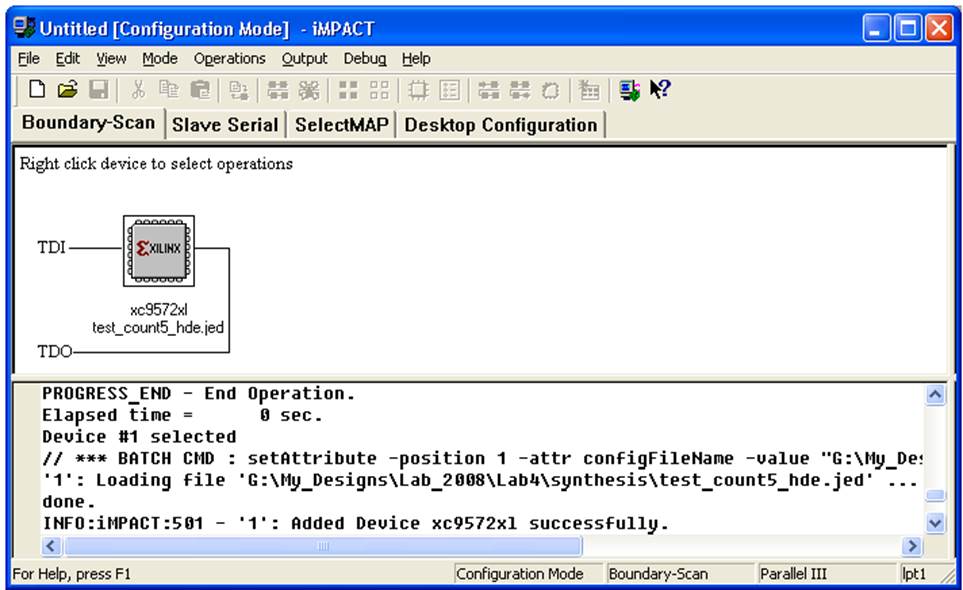

3.3. После назначения указанного конфигурационного файла откроется новая панель (рис.8), на которой показывается программируемая микросхема, её имя и название файла конфигурации.

Щёлкните правой кнопкой мыши по микросхеме и исполните команду Program…. Опции программирования оставьте такими, как они заданы по умолчанию.

Ни в коем случае не сбрасывайте флажок EraseBeforeProgramming(очищать перед программированием). Это может привести к нарушению работы ПЛИС.

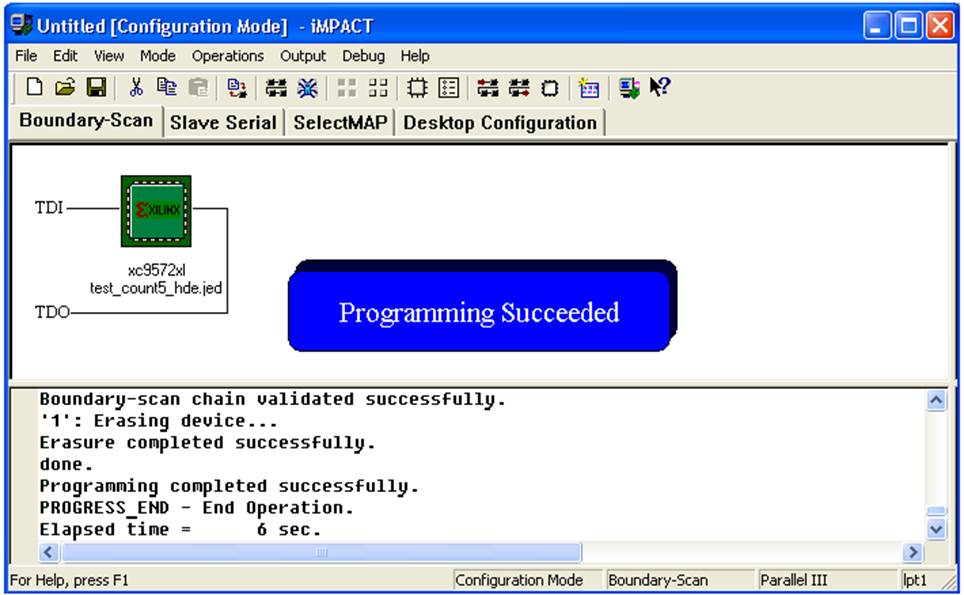

Процесс загрузки простого проекта в микросхему может занимать несколько секунд (в приведённом примере 5 сек.), и при успешном его завершении появится запись «ProgrammingSucceeded» (рис.9).

Рис.8. Программа iMPACT

определила JTAG-цепочку,

и теперь всё готово для программирования микросхемы xc9572xl

Рис.9. Успешное завершение загрузки конфигурационного файла в микросхему

3.4. Протестируйте физически реализованный проект с помощью компонентов, установленных на учебном стенде. Задавайте переключателями SW0…SW7 входные сигналы и наблюдайте на светодиодах D6…D13 и семисегментных индикаторах IND1 реакции на эти воздействия.

Убедитесь, что поведение реализованной в «железе» схемы соответствует техническому заданию на ваш проект.

ЗАДАНИЕ 4. Отладка физически реализованного проекта на учебном стенде SDK 7.1 в автоматическом режиме. Ориентировочное время выполнения задания – 30 мин. (1,0 балл).

4.1. Вернитесь в интегрированную среду проектирования Active-HDL 7.1 и добавьте к своему проекту ещё один отладочный компонент – счётчик-делитель частоты внутреннего генератора импульсов 16MHz. Он установлен на стенде SDK 7.1, но его высокая частота не позволяет визуально наблюдать работу схемы. Необходимо понизить частоту до одного – двух герц.

Для этих целей потребуется делитель частоты, содержащий 23..24 двоичных разряда.

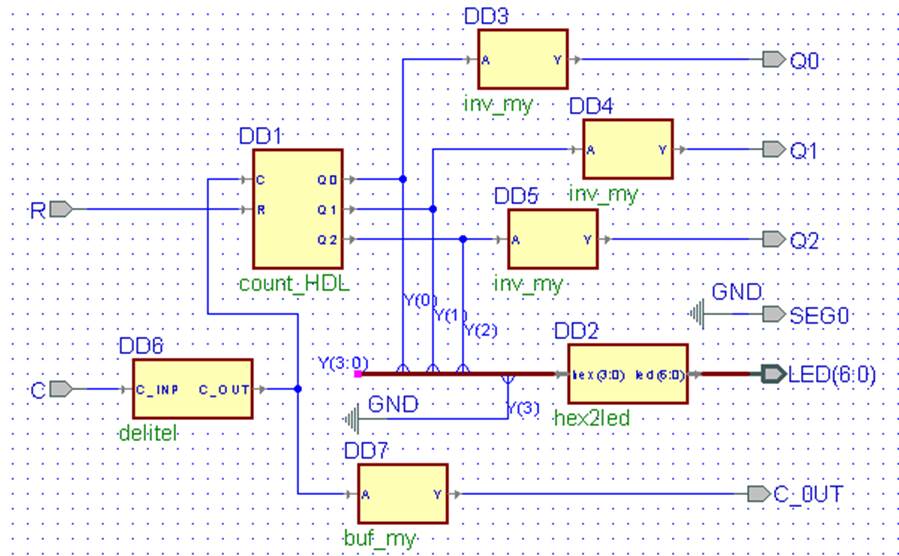

4.2. Постройте VHDL-модель такого делителя и добавьте его в свой проект (рис.10). Теперь тактирующие сигналы в вашу схему должны поступать не с механического переключателя, установленного на стенде (в примере SW7, контакт P36), а с выхода генератора импульсов, подключённого к контакту 22 программируемой микросхемы. Другими словами, входной порт C (от слова CLOCK) проекта надо ассоциировать с контактом 22 микросхемы.

Рис.10. Модифицированная схема, подготовленная для

проведения экспериментов

на стенде SDK7.1 в автоматическом режиме

На выход делителя тоже желательно подключить светодиод, например D6 (контакт P66), чтобы визуально наблюдать осциллирующий процесс. Внесите в проект названные изменения и вновь проведите функциональное моделирование. Для удобства наблюдения имитационного эксперимента число разрядов счётчика-делителя можно на время эксперимента уменьшить до 3…4 разрядов.

4.3. Вам придётся создать новую версию UCF-файла, так как в схему добавлен ещё один выходной порт C_OUT (см. рис.10).

4.4. Запустите процесс GenerateProgrammingFile, чтобы получить конфигурационный файл. Убедитесь в том , что он создан (напомню, этот файл имеет расширение *.JED и находится в папке проекта synthesis).

Перенесите его на компьютер преподавателя, к которому подключён учебный стенд SDK 7.1, и проведите загрузку конфигурационного файла в программируемую микросхему, смонтированную на стенде.

Визуально проконтролируйте функционирование вашего устройства в автоматическом режиме работы.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.