+ IO_LEVEL=0 MNTYMXDLY=0

X_DD12_DD19_1 S0_Gbar S0_G $G_DPWR $G_DGND K555LN1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD12_DD15_1 $N_0019 S0_Gbar $G_DPWR $G_DGND K555LN1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD12_DD16_1 EZ $N_0020 $G_DPWR $G_DGND K555LN1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD12_DD1 E_G S2_G S0_G S1_G D7 $D_HI $D_HI $D_HI $N_0024 $G_DPWR

+ $G_DGND K555LA2 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD12_DD3 E_G S2_G S0_G S1_Gbar D5 $D_HI $D_HI $D_HI $N_0028 $G_DPWR

+ $G_DGND K555LA2 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD12_DD5 E_G S0_G S1_G S2_Gbar D3 $D_HI $D_HI $D_HI $N_0032 $G_DPWR

+ $G_DGND K555LA2 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD12_DD11 E_G S0_G S1_Gbar S2_Gbar D1 $D_HI $D_HI $D_HI $N_0036

+ $G_DPWR $G_DGND K555LA2 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD12_DD8 $N_0024 $N_0004 $N_0028 $N_0008 $N_0032 $N_0012 $N_0036

+ $N_0016 $N_0037 $G_DPWR $G_DGND K555LA2 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD12_DD45 S2 $N_0017 $G_DPWR $G_DGND DELAY_ELEM

X_DD12_DD46 S1 $N_0018 $G_DPWR $G_DGND DELAY_ELEM

X_DD12_DD47 S0 $N_0019 $G_DPWR $G_DGND DELAY_ELEM

X_DD12_DD43 $N_0037 E_G Q $G_DPWR $G_DGND K155LP14A PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD12_DD7_1 $N_0038 E_G Qbar $G_DPWR $G_DGND K155LP14 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD12_DD9_1 $N_0037 $N_0038 $G_DPWR $G_DGND K555LN1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD12_DD48 $N_0020 E_G $G_DPWR $G_DGND DELAY_ELEM2

Рис 5. Содержимое файла verif3.net

* G:\MSim_8\Projects\kr\verif3.stl written on Thu Dec 01 11:43:31 2005

* by Stimulus Editor -- Serial Number: 100617 -- Version 8.0

;!Stimulus Get

;! D0 Digital D1 Digital D2 Digital D3 Digital D4 Digital D5 Digital D6 Digital D7 Digital S0 Digital S1 Digital S2 Digital E Digital

;!Ok

;!Plot Axis_Settings

;!Xrange 0s 4us

;!AutoUniverse

;!XminRes 50ns

;!YminRes 1n

;!Ok

.STIMULUS D0 STIM (1, 1)

+ +0s 0

+ 50ns 1

.STIMULUS D1 STIM (1, 1)

+ +0s 1

+ 150ns 0

.STIMULUS D2 STIM (1, 1)

+ +0s 0

.STIMULUS D3 STIM (1, 1)

+ +0s 1

.STIMULUS D4 STIM (1, 1)

+ +0s 0

+ 2.45us 1

.STIMULUS D5 STIM (1, 1)

+ +0s 1

.STIMULUS D6 STIM (1, 1)

+ +0s 0

.STIMULUS D7 STIM (1, 1)

+ +0s 1

.STIMULUS S0 STIM (1, 1) ;! CLOCK 4M 0.5 0 0

+ +0s 0

+ +125ns 1

+ Repeat Forever

+ +125ns 0

+ +125ns 1

+ EndRepeat

.STIMULUS S1 STIM (1, 1) ;! CLOCK 2M 0.5 0 0

+ +0s 0

+ +250ns 1

+ Repeat Forever

+ +250ns 0

+ +250ns 1

+ EndRepeat

.STIMULUS S2 STIM (1, 1) ;! CLOCK 1M 0.5 0 0

+ +0s 0

+ +500ns 1

+ Repeat Forever

+ +500ns 0

+ +500ns 1

+ EndRepeat

.STIMULUS E STIM (1, 1)

+ +0s 0

+ 800ns 1

+ 1.25us 0

+ 1.95us 1

+ 2.6us 0

Рис 6. Содержимое файла verif3.stl

Схема верификации иерархического символа представлена на рис.7.

Рис. 7. Схема верификации иерархического символа.

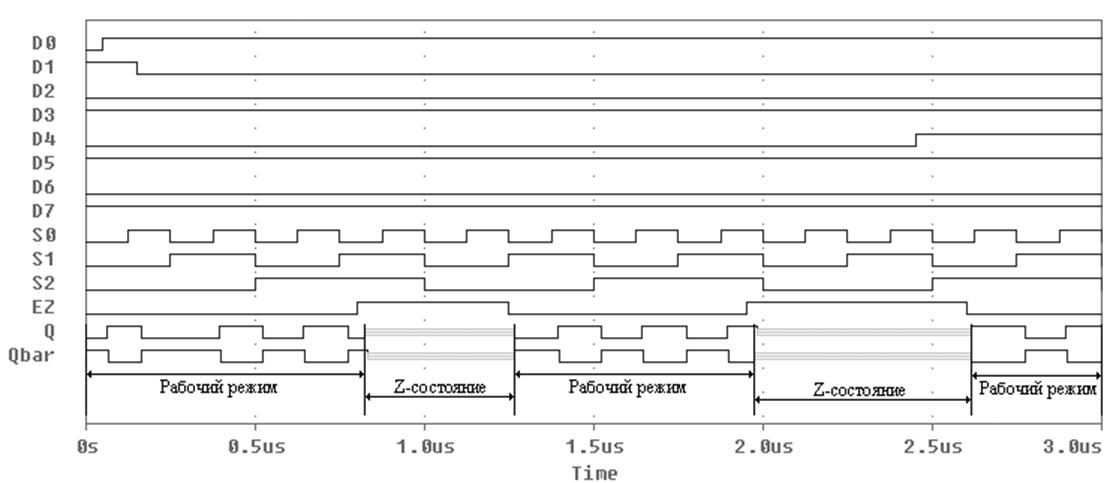

Результаты моделирования узла в виде временных диаграмм представлены на рис. 8.

Рис. 8. Результаты моделирования узла

Данный эксперимент отражает все режимы работы узла (табл. 2). Режим Z-состояния наступает при высоком уровне сигнала на входе #EZ.

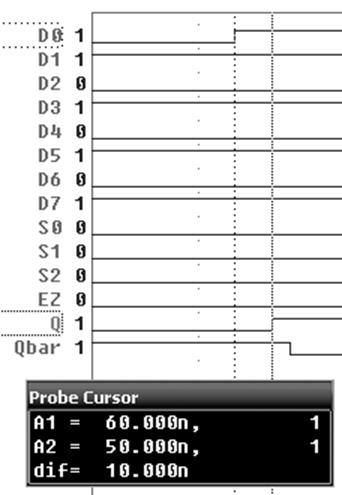

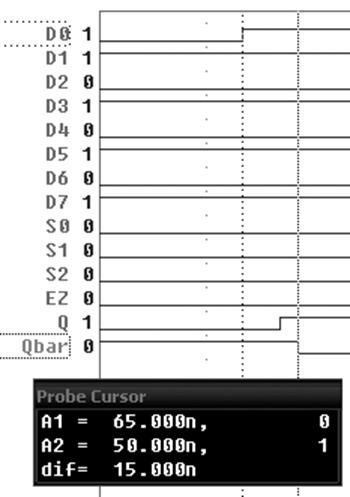

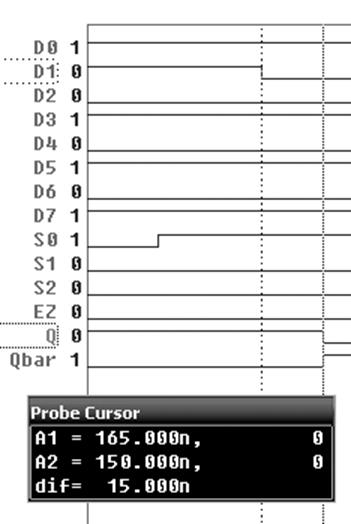

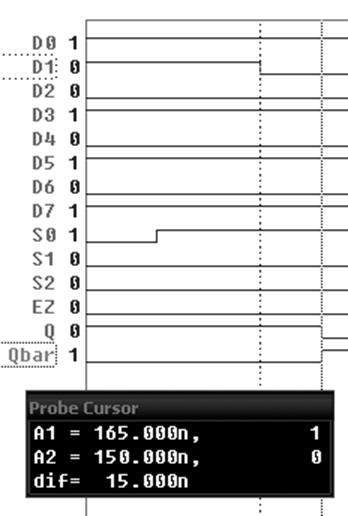

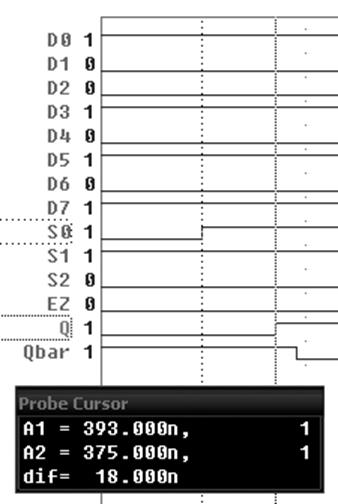

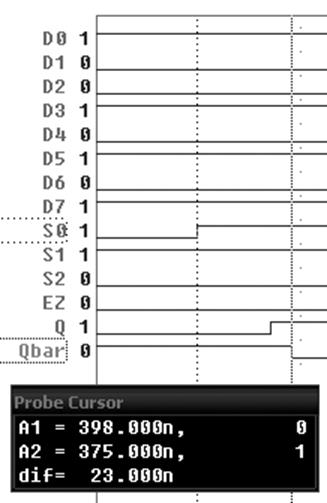

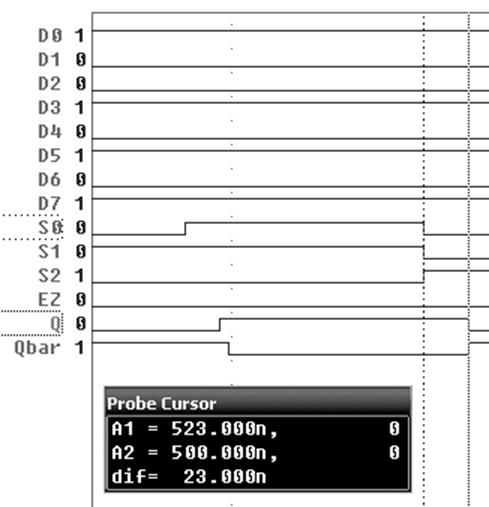

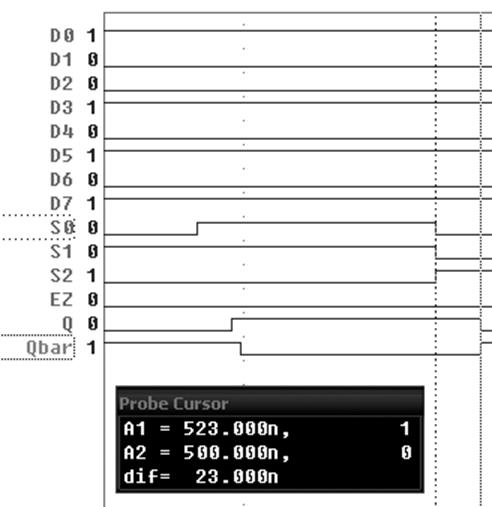

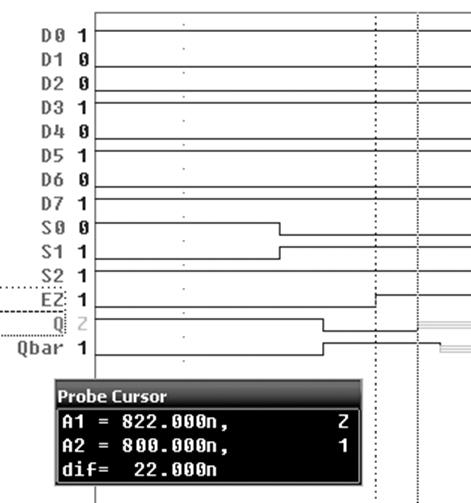

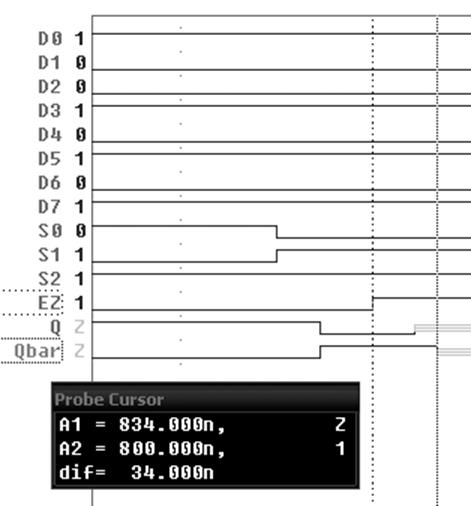

На приведённых ниже временных диаграммах показаны все случаи задержек распространения сигналов.

Рис. 9. Задержка tPLH от D для Q. Рис. 10. Задержка tPHL от D для #Q.

Рис. 11. Задержка tPHL от D для Q. Рис. 12. Задержка tPLH от D для #Q.

Рис. 13. Задержка tPLH от S для Q. Рис. 14. Задержка tPHL от S для #Q.

Рис. 15. Задержка tPHL от S для Q. Рис. 16. Задержка tPLH от S для #Q.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.