Результаты верификации символа с подключённой к нему макромоделью представлены на рис. 27.

Рис. 27. Результаты верификации символа с подключённой к нему макромоделью.

Иерархический символ проектируемого узла представлен на рис. 28.

.

.

Рис. 28. Иерархический символ проектируемого узла.

Принципиальная схема замещения проектируемого узла представлена на рис. 29.

Рис. 29. Принципиальная схема замещения проектируемого узла.

Все элементы данной схемы имеют реальные прототипы, за исключением элемента DELAY_ELEM — это абстрактный элемент задержки, не имеющий реального аналога, он используется для приведения задержек распространения сигналов к реальным. VHDL-модели всех элементов данной схемы представлены в приложении 2.

Схема верификации иерархического символа представлена на рис.30.

Рис. 30. Схема верификации иерархического символа.

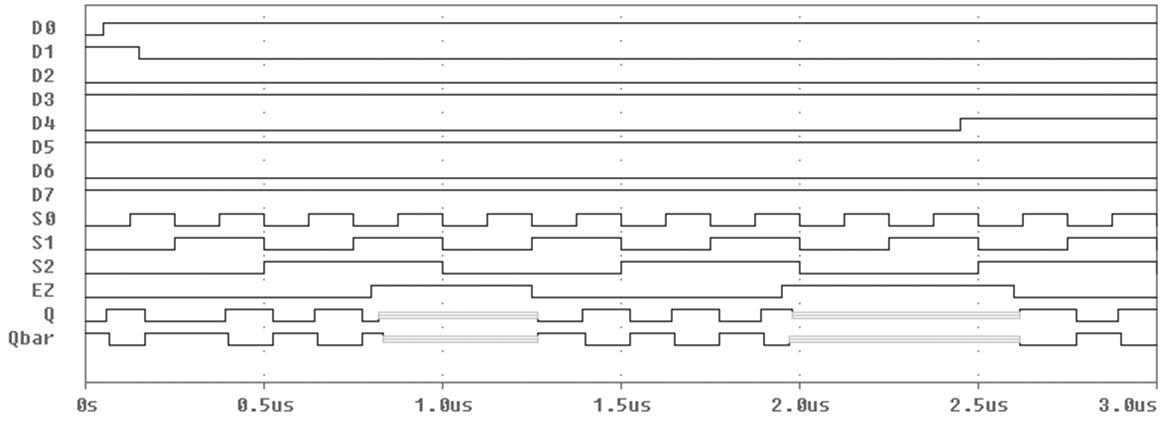

Результаты моделирования узла в виде временных диаграмм представлены на рис. 31.

Рис. 31. Результаты моделирования узла

Данный эксперимент отражает все режимы работы узла (табл. 2). Режим Z-состояния наступает при высоком уровне сигнала на входе #EZ.

На приведённых ниже временных диаграммах показаны все случаи задержек распространения сигналов (некоторые задержки помещены на общие диаграммы для экономии места).

Рис. 32. Задержка tPLH от D для Q (10 нс.). Рис. 33. Задержка tPHL от D для #Q (15 нс.).

Рис. 34. Задержки tPLH от D для #Q и tPHL для Q (15 нс.). Рис. 35. Задержка tPLH от S для Q (18 нс.).

Рис. 36. Задержка tPHL от S для #Q (23 нс.). Рис. 37. Задержки tPHL от S для Q и tPLH для #Q (23 нс.).

Рис. 38. Задержка tPHZ для Q (31 нс.). Рис. 39. Задержка tPLZ для #Q (22 нс.).

Рис. 40. Задержки tPZL для Q и tPZH для #Q (15 нс.). Рис. 41. Задержки tPHZ для Q (31 нс.) и

tPLZ для #Q (22 нс.).

LIBRARY ieee; --подключение необходимых библиотек

USE ieee.std_logic_1164.all;

USE work.orcad_prims.all;

ENTITY \KR1533KP15M\ IS PORT( --описание входов и выходов узла

D0 : IN std_logic;

D1 : IN std_logic;

D2 : IN std_logic;

D3 : IN std_logic;

D4 : IN std_logic;

D5 : IN std_logic;

D6 : IN std_logic;

D7 : IN std_logic;

S0 : IN std_logic;

S1 : IN std_logic;

S2 : IN std_logic;

NEZ : IN std_logic;

Q : OUT std_logic;

NQ : OUT std_logic);

END \KR1533KP15M\;

ARCHITECTURE model OF \KR1533KP15M\ IS

signal S : std_logic_vector(2 downto 0); --вектор, используемый для объединения

--управляющих сигналов

SIGNAL Q1: std_logic; --переменные для хранения выходных

SIGNAL NQ1: std_logic; --значений

BEGIN

S <= S2&S1&S0; --инициализация вектора S

PROCESS(NEZ,D0,D1,D2,D3,D4,D5,D6,D7,S)

variable PREQ: std_logic;

BEGIN

IF (S="000") THEN PREQ := D0; --выбор данных, соответствующих

ELSIF (S="001") THEN PREQ := D1; --входным управляющим сигналам

ELSIF (S="010") THEN PREQ := D2;

ELSIF (S="011") THEN PREQ := D3;

ELSIF (S="100") THEN PREQ := D4;

ELSIF (S="101") THEN PREQ := D5;

ELSIF (S="110") THEN PREQ := D6;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.