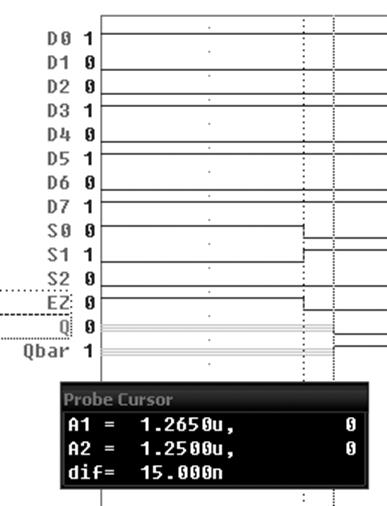

Рис. 17. Задержка tPLZ для Q. Рис. 18. Задержка tPHZ для #Q.

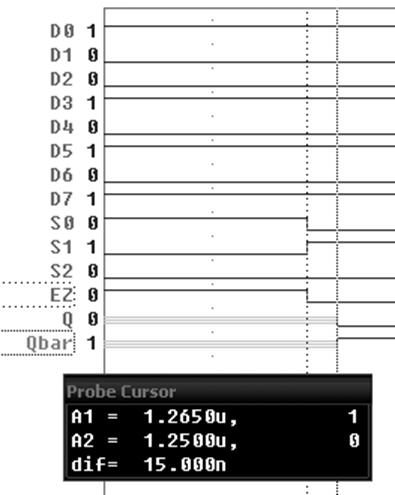

Рис. 19. Задержка tPZL для Q. Рис. 20. Задержка tPZH для #Q.

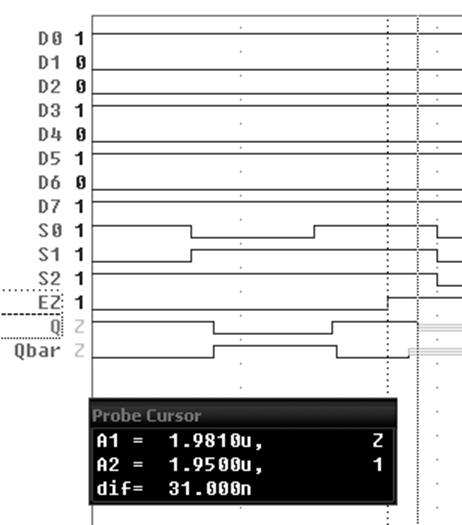

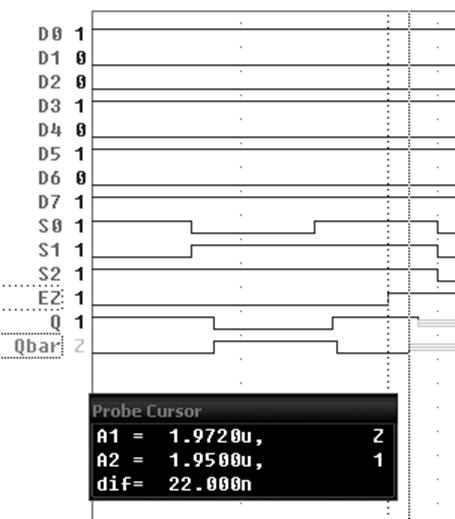

Рис. 21. Задержка tPHZ для Q. Рис. 22. Задержка tPLZ для #Q.

Предельная частота изменения сигналов на входах узла (он является комбинационной схемой) – величина, обратная максимальной задержке распространения сигнала от входа до выхода. Максимальная задержка — tPHZ для выхода #Q составляет 34нс.

fmax = 1 / tPHZ = 1 / 34нс = 29,4 МГц

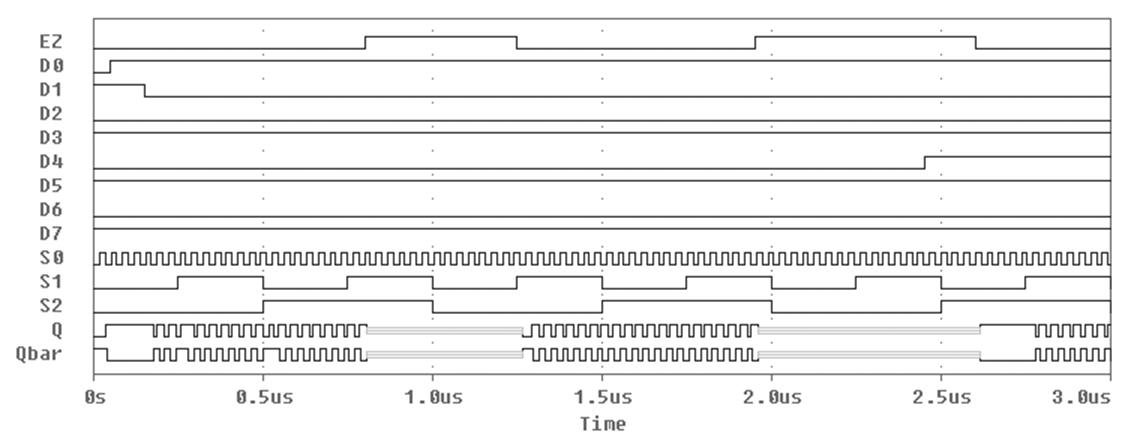

Временная диаграмма работы узла при изменении сигнала на входе S0 с частотой

29,4 МГц представлена на рис. 23.

Рис. 23. Временная диаграмма работы узла при изменении сигнала на входе S0 с частотой 29.4 МГц.

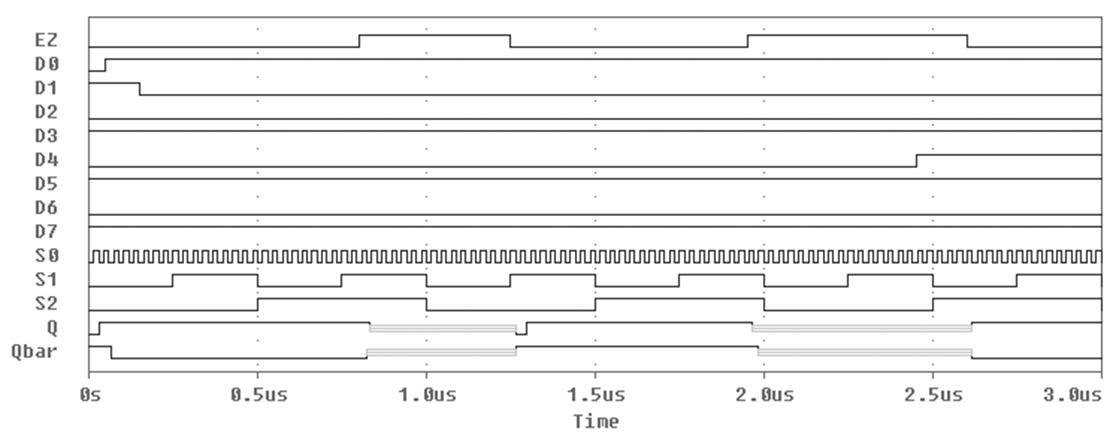

Протестируем работу узла на недопустимой по расчётам частоте в 34Мгц. Результаты тестирования приведены на рис. 24.

Рис. 24. Временная диаграмма работы узла при изменении сигнала на входе S0 с частотой 34 МГц.

Как видно по диаграмме, узел работает некорректно — теоретические расчёты подтвердились.

* KR1533KP15M MULTIPLEXER/DATA SELECTOR 8-1 LINE WITH 3-STATE OUTPUTS

*

* ALS/AS LOGIC CIRCUITS DATA BOOK, 1986, TI

* TC 08/24/92 REMODELED USING LOGICEXP, PINDLY, & CONSTRAINT DEVICES

*

.SUBCKT KR1533KP15M GBAR_I A_I B_I C_I D0_I D1_I D2_I D3_I D4_I D5_I D6_I D7_I

+ Y_O W_O

+ OPTIONAL: DPWR=$G_DPWR DGND=$G_DGND

+ PARAMS: MNTYMXDLY=0 IO_LEVEL=0

*

UKR1533KP15MLOG LOGICEXP(12,14) DPWR DGND

+ GBAR_I A_I B_I C_I D0_I D1_I D2_I D3_I D4_I D5_I D6_I D7_I

+ GBAR A B C D0 D1 D2 D3 D4 D5 D6 D7 W Y

+ D0_GATE IO_ALS00 IO_LEVEL={IO_LEVEL}

+ LOGIC:

+ GBAR = { GBAR_I }

+ A = { A_I }

+ B = { B_I }

+ C = { C_I }

+ D0 = { D0_I }

+ D1 = { D1_I }

+ D2 = { D2_I }

+ D3 = { D3_I }

+ D4 = { D4_I }

+ D5 = { D5_I }

+ D6 = { D6_I }

+ D7 = { D7_I }

+ IA = { ~A }

+ IB = { ~B }

+ IC = { ~C }

+ ID0 = { D0 & IA & IB & IC }

+ ID1 = { D1 & A & IB & IC }

+ ID2 = { D2 & IA & B & IC }

+ ID3 = { D3 & A & B & IC }

+ ID4 = { D4 & IA & IB & C }

+ ID5 = { D5 & A & IB & C }

+ ID6 = { D6 & IA & B & C }

+ ID7 = { D7 & A & B & C }

+ W = { ~(ID0 | ID1 | ID2 | ID3 | ID4 | ID5 | ID6 | ID7) }

+ Y = { ~W }

*

UKR1533KP15MDLY PINDLY (2,1,11) DPWR DGND

+ W Y

+ GBAR

+ A B C D0 D1 D2 D3 D4 D5 D6 D7

+ W_O Y_O

+ IO_ALS00 MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL}

+ BOOLEAN:

+ DATA = { CHANGED(D0,0) | CHANGED(D1,0) | CHANGED(D2,0) | CHANGED(D3,0) |

+ CHANGED(D4,0) | CHANGED(D5,0) | CHANGED(D6,0) | CHANGED(D7,0) }

+ SELECT = { CHANGED(A,0) | CHANGED(B,0) | CHANGED(C,0) }

+ TRISTATE:

+ ENABLE LO GBAR

+ Y_O = {

+ CASE(

+ SELECT & TRN_HL, DELAY(8NS,-1,23NS),

+ SELECT & TRN_LH, DELAY(5NS,-1,18NS),

+ TRN_Z$, DELAY(3NS,-1,15NS),

+ DATA & TRN_HL, DELAY(3NS,-1,15NS),

+ DATA & TRN_LH, DELAY(2NS,-1,10NS),

+ TRN_HZ, DELAY(2NS,-1,31NS),

+ TRN_LZ, DELAY(1NS,-1,22NS),

+ DELAY(9NS,-1,25NS)

+ )

+ }

+ W_O = {

+ CASE(

+ SELECT & TRN_LH, DELAY(8NS,-1,23NS),

+ SELECT & TRN_HL, DELAY(7NS,-1,23NS),

+ DATA, DELAY(3NS,-1,15NS),

+ TRN_Z$, DELAY(3NS,-1,15NS),

+ TRN_HZ, DELAY(2NS,-1,34NS),

+ TRN_LZ, DELAY(1NS,-1,22NS),

+ DELAY(9NS,-1,25NS)

+ )

+ }

*

.ENDS

*

*$

Рис. 25. Функциональное описание проектируемого узла с помощью примитивов LOGICEXP, PINDLY и CONSTRAINT.

Схема верификации символа с подключённой к нему макромоделью представлена на рис. 26.

Рис. 26. Схема верификации символа с подключённой к нему макромоделью.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.