Введение в стандарт IEEE. Справочное руководство по языку VHDL (Пересмотр стандарта IEEE. 1076-1987):

Very High Speed Integrated Circuit (VHSIC) Hardware Description Language (VHDL) - формальная система обозначений, предназначенная для использования на всех стадиях создания электронных систем. Описание созданное с помощью этих обозначений понятно как человеку, так и машине, оно поддерживает проверку, синтез, и испытание аппаратных конструкций, связывает эксплуатационные и аппаратных данные.

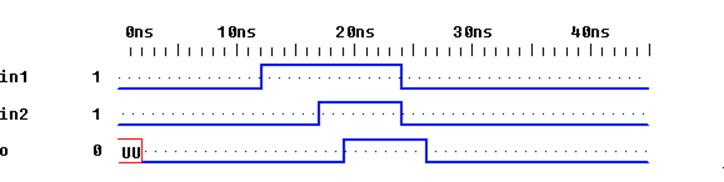

Из-за своей гибкости, VHDL может использоваться в различных случаях. Поскольку язык описывает поведение аппаратной логики, это может использоваться как для имитационных моделей, так и для композиции конструкций. Для примера, рассмотрим исходный текст, моделирующий простую конъюнкцию:

o <= in1 and in2 after 2 ns;

|

Диаграмма работы подтверждает функцию модели. Тот же самый исходный текст можно передать в таком виде логическому синтезатору или транслятору, для преобразования в специальный элемент. Синтезатор генерирует список соединений, как показано ниже, которые определяют элемент:

SYM, U1, AND, LIBVER=2.0.0

PIN, I0, I, IN1

PIN, I1, I, IN2

PIN, O, O, _O_

END

Специальный транслятор воспринимает текст на VHDL, схемные решения и создает уровни компонентов и список соединений, подобных образцу выше. Языки для описания аппаратных конструкций, САПР электронных устройств (EDA) и технология синтеза - результат потребности в расширенной аппаратной методологии конструкций, для проектирования ИС и СБИС. Синтез САПР электронных устройств и инструментальных средств оптимизации дает возможность создавать языки высокого уровня (типа VHDL), как входные, с помощью которых на выходе можно получать листинг сети логических вентилей и соединителей.

Существует несколько преимуществ использования VHDL для аппаратной конструкции:

1. Абстрагирование конструкции. Логическая конструкция, использующая абстрактный язык описания аппаратуры, подобный VHDL, повышает производительность, позволяя проектировщику работать с терминами логических операций и поведения, что удобнее, чем традиционный подход рисования коммутационных схем логических вентилей и соединений.

2. Улучшенная документация и качество. Разработка на VHDL поощряет имитацию. В дополнение к очевидным выгодам от отладки логики, исходный текст на VHDL испытательного стенда, помогает документировать поведение конструкции. Т.е. описываются входы, и ожидаемые выходы конструкции, что облегчает обслуживание конструкции в будущем.

3. Взаимозаменяемость конструкции. Возможно, это наиболее веская причина для принятия стандарта языка проектов, чтобы легко переносить исходную конструкция от одного продавца программируемого логического устройства или ИС к другому. Схематически основанные конструкции обычно зафиксированы в терминах программируемого логического устройства, специализированные логические символы которых требуют капитальных изменений для перенастройки.

Программирование логического проекта сверху - вниз.

На диаграмме ниже изображен типичный поток при программировании логического проекта. Поток проекта начинается на фазе ввода проекта с создания описания аппаратных средств, обычно для этого используется VHDL или схемное решение. После того, как вы ввели проект, используется первая, моделирующая фаза (в проекте), для отладки схемного решения и ресурсов проекта. На фазе компиляции происходит синтез и оптимизация, для преобразования описания проекта к схеме логических функций. Фаза компоновки разбивает проект на специфические программируемые устройства. В течение заключительной фазы моделирования, проверяется пост-маршрут проекта, выполнение требований работы проекта.

|

Комбинационная логика.

Булевы уравнения - самые простые и наиболее универсальные конструкции в VHDL. В таблице ниже представлены булевы уравнения, соответствующие им VHDL эквиваленты, и логические операции.

Булевы уравнения |

VHDL эквивалент |

Операция |

|

Y1 = (A1)(B1) |

y1 <= a1 and b1; |

И |

|

Y2 = A2 + B2 |

y2 <= a2 or b2; |

ИЛИ |

|

Y3 = A3 |

y3 <= a3 xor b3; |

Исключающее ИЛИ |

|

Y4 = (A4)' |

y4 <= not(a4); |

НЕ |

|

Y5 = ((A5)(B5))' |

y5 <= a5 nand b5; |

НЕ-И |

|

Y6 = ((A6)+(B6)) |

y6 <= a6 nor b6; |

НЕ-ИЛИ |

При схемном решении, сигналы представляются проводами или шинами, а их прохождение - графическими символами. В VHDL, сигналы объявляются в соответствии с функциональными возможностями, которые реализуются операторами И и ИЛИ.

Исходный текст ниже - полная модель уравнений, которую в дальнейшем вы можно использовать, для моделирования, отладки или синтеза.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.