Если селекторное значение - индекс массива, селектор будет превращен в мультиплексор. Это можно выразить в операторе выбора, но также возможно использовать переменную индексированного массива. Например, если индексы массива целые, индексная переменная массива создаст функцию мультиплексора:

signal vec : std_logic_vector (0 to 15) ;

signal o : std_logic ;

signal i : integer range 0 to 15 ;

...

o <= vec(i) ;

Выбор бита i из вектора vec можно записать короче при помощи оператора выбора:

case i is

when 0 => o <= vec(0) ;

when 1 => o <= vec(1) ;

when 2 => o <= vec(2) ;

when 3 => o <= vec(3) ;

...

end case ;

Для предшествующего описания, инструментальные средства синтеза создают те же самые мультиплексоры, поскольку они делают это для индексной переменной массива.

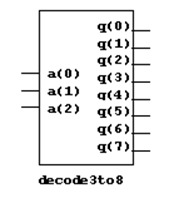

Декодеры.

Этот раздел описывает подход к созданию декодеров. Вы можете создавать систему булевых уравнений описывающих декодер, используя VHDL циклы и индексы. Ниже вы найдете пример построения логического декодера.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity decoder is

port (a : unsigned (2 downto 0);

q : out unsigned (7 downto 0));

end;

architecture behavior of decoder is

begin

process (a)

begin

for i in natural range 7 downto 0 loop

if (a=i) then

q(i) <= '1';

else

q(i) <= '0';

end if;

end loop;

end process;

end behavior;

Далее вы найдете более компактную запись для, описания системы булевых уравнений, которая используется для циклов в VHDL, при описании индексированных уравнений. Рассмотрим исходный текст, для схемы 4И с двумя входами.

Y1 <= A1 and B1;

Y2 <= A2 and B2;

Y3 <= A3 and B3;

Y4 <= A4 and B4;

Эта же схема 4И может быть описана единственным уравнением в пределах цикла на VHDL.

for i in 1 to 4 loop

Y(i) <= A(i) and B(i);

end loop;

Эти две только что описанные схемы 4И идентичны, но имеется более простой путь к индексированной форме. Рассмотрим таблицу истинности для декодера 3:8.

|

|

ВХОДЫ |

ВЫХОДЫ |

|

A |

q |

|

000 |

00000001 |

|

001 |

00000010 |

|

010 |

00000100 |

|

011 |

00001000 |

|

100 |

00010000 |

|

101 |

00100000 |

|

110 |

01000000 |

|

111 |

10000000 |

Чтобы составить на VHDL решение этой таблицы, начнем с уравнения для q0 и q1.

if (a=b"000") then

q(0) <= '1';

else

q(0) <= '0';

end if;

if (a=b"001") then

q(1) <= '1';

else

q(1) <= '0';

end if;

Выходы q0 и q1 активны, если все три входа неактивны, и если на все три входа поданы 1. Используя эти основные уравнения, как руководство мы можем записать общее описание и заменить индексы в цикле на похожие значения индексов выхода q.

В VHDL источник подобен комбинационной логической модели, представленной ранее, только теперь поведение содержится в процессе VHDL. Обратите внимание, что список чувствительности включает сигнал, установки “a”, кроме того все входные сигналы комбинационных процессов должны быть включены в список чувствительности.

В качестве альтернативы можно в процедуре, кодирующей стиль использовать параллельные присвоения сигнала вместо последовательных в пределах процесса. Пример ниже описывает конструкцию для создания 8 уравнений: с dec(7) до dec(0).

--- 3:8 decoder

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity decoder is

port(a: in std_logic_vector(2 downto 0);

dec: out std_logic_vector(7 downto 0));

end;

architecture behavior of decoder is

begin

a_dec: for n in natural range 7 downto 0 generate

dec(n) <= '1' when unsigned(a)=n else

'0';

end generate;

end;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.