B2: block (CLK'event and CLK='1')

begin

Q_OUT <= guarded DATA ;

end block ;

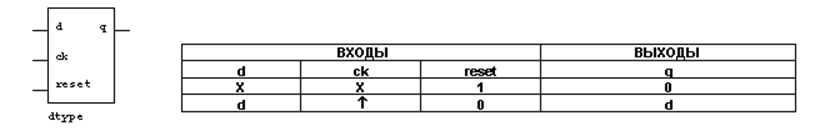

Сброс и предварительная установка.

Этот раздел описывает процедуру, сброса и предварительной установки регистра в VHDL. Еще два общих управляющих сигнала триггера - это асинхронный сброс и синхронная предварительная установка. Асинхронное управление подразумевает, что, независимо от длительности такта, триггер реагирует, если асинхронный сигнал активен. У большинства логических устройств асинхронный сброс, обнуляет (0) Q-вывод триггера. Так как логика сброса независима от логики синхронизации, она добавляется к списку чувствительности процесса VHDL, и новая конструкция if - then определяется вне контекста логики синхронизации, чтобы управлять обнулением вывода, когда происходит сброс.

|

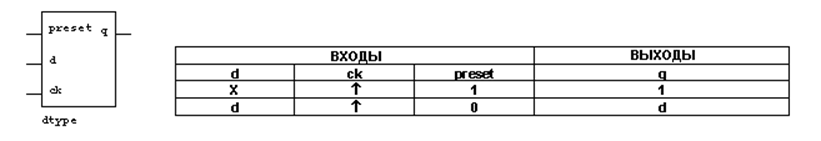

Синхронное управление на триггере осуществляется до того момента как триггер изменит свое состояние, зависящее от импульса синхронизации. Большинство программируемых логических устройств содержат синхронное программное управление, которое приводит Q-вывод триггера к единице (1). Так как логика предварительной установки зависит от логики синхронизации, новая VHDL конструкция if - then определяется внутри контекста логики синхронизации, чтобы управлять приведением к единице (1) выхода-Q, если подан сигнал предварительной установки.

|

Общий стиль для D-триггеров со сбросом и предварительной установкой показан ниже.

D-триггер с синхронной предварительной установкой:

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity dtype is

port (d, ck, preset : std_logic;

q : out std_logic);

end;

architecture behavior of dtype is

begin

process (d, ck, preset)

begin

if (ck = '1') and ck'event then

if (preset = '1') then

q <= '1';

else

q <= d;

end if;

end if;

end process;

end behavior;

D-триггер с асинхронным сбросом:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity dtype is

port (d, ck, reset : std_logic;

q : out std_logic);

end;

architecture behavior of dtype is

begin

process (d, ck, reset)

begin

if reset = '1' then

q <= '0';

elsif ck = '1' and ck'event then

q <= d;

end if;

end process;

end behavior;

В качестве альтернативы определения синхронного сигнала предварительной установки можно использовать, инструкции потока данных, например, используя блок GUARDED и условное назначение сигнала.

B3: block (CLK'event and CLK='1')

begin

Q_OUT <= guarded '1' when PRESET='1' else DATA;

end block ;

Асинхронная предварительная установка и сброс, могут использоваться вместе. Также можно составлять выражения, вместо фиксированного '0' или '1' в операциях присвоения на Q_OUT, в сбросе и предварительной установке состояния. Это приводит к комбинационной логике, описывающей набор, и сбросу целевого сигнала входа триггера. Следующий фрагмент показывает структуру такого процесса:

process (clock, asynchronously_used_signals )

begin

if (boolean_expression) then

asynchronous signal_assignments

elsif (boolean_expression) then

asynchronous signal_assignments

elsif (clock'event and clock = constant ) then

synchronous signal_assignments

end if ;

end process ;

Могут иметься несколько асинхронных elsif предложений, но синхронное elsif предложение должно быть последним в условном операторе. Триггер должен быть описан для каждого сигнала, назначенного в описании синхронного сигнала. Асинхронные предложения приводят к комбинационной логике, которая управляет набором и сбрасывать вводы триггера. Если не имеется никакой оговорки о синхронизации, вся логика становится комбинационной.

Возможности синхронизации.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.