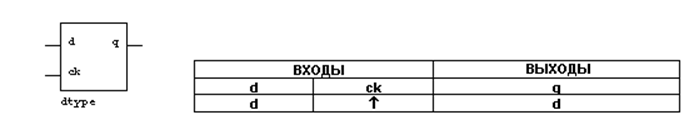

Этот раздел описывает создание синхронного триггера в VHDL. Примеры показывают схемное решение и VHDL эквиваленты.

Большинство программируемых топологических элементов прибора это регистры или элементы памяти, которые могут быть описаны с помощью D-триггеров. Пример ниже иллюстрируют разнообразные стили описания регистров.

|

Общий стиль для D-триггера имеет вид:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity dtype is

port (d, ck : std_logic;

q : out std_logic);

end;

architecture behavior of dtype is

begin

process (d, ck)

begin

if ck = '1' and ck'event then

q <= d;

end if;

end process;

end behavior;

Альтернативой, может быть более компактный подход:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity dtype is

port (d, ck : std_logic;

q : out std_logic);

end;

architecture behavior of dtype is

begin

process

begin

wait until ck'event and ck='1';

q <= d;

end process;

end behavior;

Примеры выше выводят повышающиеся фронты синхроимпульса. Чтобы определить падение на границе синхроимпульсов, скорректируйте выражение VHDL, которое описывает состояние синхроимпульса:

if ck = '0' and ck'event then ...

Использование в портах данных типа std_logic. Тип данных std_logic - привилегированный тип данных, для связи между VHDL и схематическими модулями проекта. Девять состояний, изображаемые типами данных учитывают изображение наиболее общих цифровых состояний системы и позволяют варьировать решение, когда множественные выводы управляются общим узлом, как в шине передачи данных. Модель dtype включает три std_logic порта типа: d, ck, и q.

Включение входных сигналов в список чувствительности процессов VHDL. Вообще, все сигналы и порты, используемые в правой стороне выражений, в пределах процесса VHDL должны быть включены в список чувствительности того процесса. В первом примере образец архитектуры dtype включает один процесс со списком чувствительности: d и ck.

Триггеры и регистры могут также быть сгенерированы при помощи инструкций потока данных (в противоположность процессу) с использованием блока GUARDED.

b2 : block (ck'event and ck='1')

begin

output_foo <= GUARDED input_foo ;

end block ;

Прибавляя инструкцию GUARDED, мы всталяем триггер между input_foo и output_foo, так как output_foo выражение блока определяющее фронт синхроимпульса.

Регистровые банки.

Переменные (подобно сигналам) могут также генерировать триггер. Так как переменная определена в процессе непосредственно, ее значение никогда не изменяется в процессе, единственный случай это когда создан триггер и переменная используется прежде, чем это определено в синхронизированном процессе. Например, следующий сегмент кода генерирует трех - разрядный сдвиговый регистр:

signal DATA,Q_OUT, CLK: std_logic;

...

process (CLK)

variable A,B: std_logic ;

begin

if (CLK'event and CLK='1') then

Q_OUT <= B ;

B := A ;

A := DATA ;

end if ;

end process ;

В этом случае, переменные A и B используются прежде, чем они определены. Поэтому, они передают значения от последнего запущенного процесса, в котором определено значение, задержанное на один тактовый цикл. Если переменные определены прежде, чем они используются, вы получите другую программу:

signal DATA,Q_OUT,CLK: std_logic;

...

process (CLK)

variable A,B: std_logic;

begin

if (CLK'event and CLK='1') then

A := DATA ;

B := A ;

Q_OUT <= B ;

end if ;

end process ;

Использование переменных может привести к неожиданным результатам. Здесь, A и B определены прежде, чем используется, и поэтому не генерируют триггер. Вместо этого, они генерируют провод. Только один триггер остается между DATA и Q_OUT из-за назначения сигнала в синхронизированном процессе.

Триггер и регистры могут также быть сгенерированы при помощи инструкций потока данных (в противоположность процессу) при использовании блока GUARDED.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.