constant Waiting : std_logic_vector(1 downto 0) := "00";

constant Ack1 : std_logic_vector(1 downto 0) := "01";

constant Ack2 : std_logic_vector(1 downto 0) := "10";

constant Ack3 : std_logic_vector(1 downto 0) := "11";

signal current_state, next_state : std_logic_vector(1 downto 0);

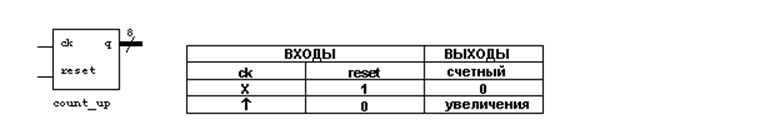

Счетчики.

Счетчики обычно представляются в виде ступенчатой последовательности состояний, у которых "спад частотной характеристики" возвращает их к начальному состоянию. В VHDL, счетчики обычно описываются с блоком регистра, который синхронизирует их с системными часами и применяет другое средство управления, типа предварительной установки или сброса. Каждый активный переход часов вызывает замену текущего индекса на следующий.

|

|

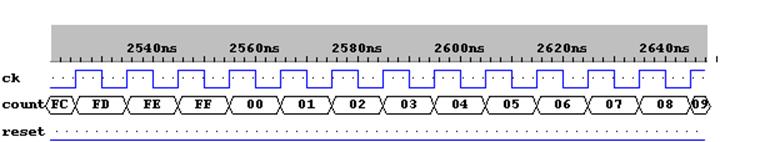

Например, см. код count_up ниже.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity count_up is

port(reset, ck : in std_logic;

count : out std_logic_vector(7 downto 0));

end;

architecture behavior of count_up is

signal count_n: unsigned(7 downto 0);

begin

process (reset, ck, count_n)

begin

if reset='1' then

count_n <= x"00";

elsif (ck='1' and ck'event) then

count_n <= count_n + "1";

end if;

end process;

count <= std_logic_vector(count_n);

end;

Как только системные часы (ck) переключаются, выходной сигнал (индекс) изменяется, увеличивая свое состояние на единицу.

|

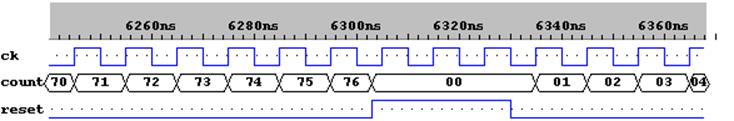

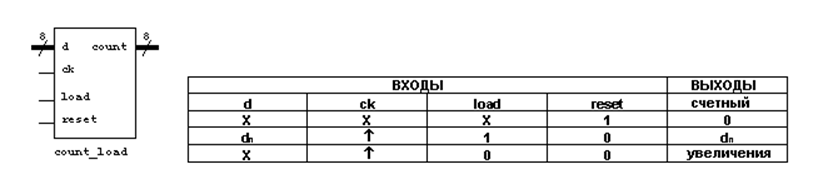

Если сигнал сброса (сброс) активен, счетчик должен обнулится. Сигнал называется асинхронным (или независимым от часов) если он находится вне логики часов. “ Стиль исходного текста" очень походит на подход, при моделировании триггеров D-типа. Счетчик загружается произвольным значением, “ встречный код загрузки “ используя набор линий данных, определенных как DATA.

|

dn - указывает состояние соответствующего входа при активном переходе часов.

Вы можете создавать счетчики, использующие двойные процессы (один, представляет комбинационную логику для декодирования индексов, другой представляет блок регистров для синхронизации индексов с часами системы).

Сложные счетчики, которые имеют доступ к часам, загружающим синхронное средство предварительной установки управления лучше создавать с блоком комбинационной логики, чтобы декодировать следующий индекс, плюс блок регистров, чтобы сохранять текущий индекс и синхронизировать с часами системы - подобный стиль описан в разделе Построение конечных автоматов.

Счетчики запускаемые положительным фронтом сигнала с дополнительным доступом к часами, и доступом к счету устанавливают, синхронную очистку, и синхронную загрузку. Следующий пример описывает 8-разрядный загружаемый счетчик обратного действия с асинхронной очисткой и доступными часами:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use WORK.EXEMPLAR_1164.all;

entity CNT_DN_AC_SL_EN is

port (CLK,CLK_EN,ACLEAR,SLOAD: in std_logic;

DATA: in std_logic_vector(7 downto 0);

Q: out std_logic_vector(7 downto 0));

end CNT_DN_AC_SL_EN;

architecture EX of CNT_DN_AC_SL_EN is

signal Q_INT: std_logic_vector(Q'range);

begin

process (CLK,ACLEAR)

begin

if (ACLEAR='1') then

Q_INT <= (Q_INT'range => '0');

elsif (CLK'event and CLK'last_value='0' and CLK='1') then

if (CLK_EN='1') then

if (SLOAD='1') then

Q_INT <= DATA;

else

Q_INT <= Q_INT - "1";

end if;

end if;

end if;

end process;

Q <= Q_INT;

end EX;

Эта модель использует пакет EXEMPLAR_1164 для оператора вычитания. Если вы хотите отмоделировать этот пример, добавьте указанный пакет к папке библиотек проекта.

Блоки регистра.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.