|

Операция |

Оператор VHDL |

Разрядность результата |

|

абсолютное значение |

abs |

та же, что и у операнда |

|

сложение |

+ |

Больше, чем у операнда |

|

вычитание |

- |

Больше, чем у операнда |

|

умножение |

* |

Сумма разрядностей операндов |

|

деление |

/ |

та же, что и у делимого |

|

целая часть |

mod |

та же что и у второго операнда |

|

остаток от деления |

rem |

та же что и у второго операнда |

Совместное использование ресурса.

Инструментальные средства синтеза автоматически выполняют устранение общих подвыражений для булевых и арифметических выражений. Следующий пример кода содержит два сумматора, которые складывают одинаковые числа a и b.

signal a,b,c,d : integer range 0 to 255 ;

...

process (a,b,c,d) begin

if ( a+b = c ) then <statements>

elsif ( a+b = d) then <more_statements>

end if ;

end process ;

Правильное использование круглых скобок приводит к тому, что инструментальные средства синтеза устраняют общие подвыражения. Следующий фрагмент кода можно изменить так, чтобы использовать один сумматор совместно.

o1 <= a + b + c;

o2 <= b + c + d;

Вставив круглые скобки, можно использовать совместно сумматор для входов b и с, как показано ниже.

o1 <= a + (b + c);

o2 <= (b + c) + d;

Инструментальные средства синтеза автоматически накладывают ограничение на количество совместного использования ресурса для арифметических выражений, которые являются взаимоисключающими. Рассмотрим следующий пример:

process (a,b,c,test) begin

if (test=TRUE) then

o <= a + b ;

else

o <= a + c ;

end if ;

end process ;

Первоначально созданы, два сумматора и мультиплексор, но после того как ресурс, совместно использующий один сумматор, автоматически уменьшен, код примет следующий вид:

process (a,b,c,test) begin

variable tmp : integer range 0 to 255 ;

begin

if (test=TRUE) then

tmp := b ;

else

tmp := c ;

end if ;

o <= a + tmp ;

end process ;

Ограничения на использование автоматического ресурса, следующие:

· Сложные операторы должны управлять тем же самым сигналом.

· Сложные операторы должны иметь одинаковый тип (например, два сумматора) и иметь одинаковую разрядность (например, 8-разрядные сумматоры).

Примеры приложений.

Далее вы можете найти примеры описания на языке VHDL общих микро функций, которые используются в цифровом логическом проекте, включая блоки регистра, счетчики, сдвиговые регистры, и конечные автоматы.

Построение конечных автоматов.

Логическая модель конечного автомата имеет входные управляющие воздействия и ответы на выходе, также она имеет несколько битов внутренней памяти, чтобы следить за самыми последними событиями. Конечный автомат использует синхронизацию, чтобы одновременно перейти на один шаг.

В VHDL конечные автоматы обычно описываются вместе с комбинационным блоком, который декодирует и управляет текущим и следующим состоянием, плюс блок регистра, чтобы синхронизировать машину с часами системы и применять другое средство управления типа предварительной установки или сброса. Каждый активный переход часов вызывает изменение текущего состояния на следующее состояние.

|

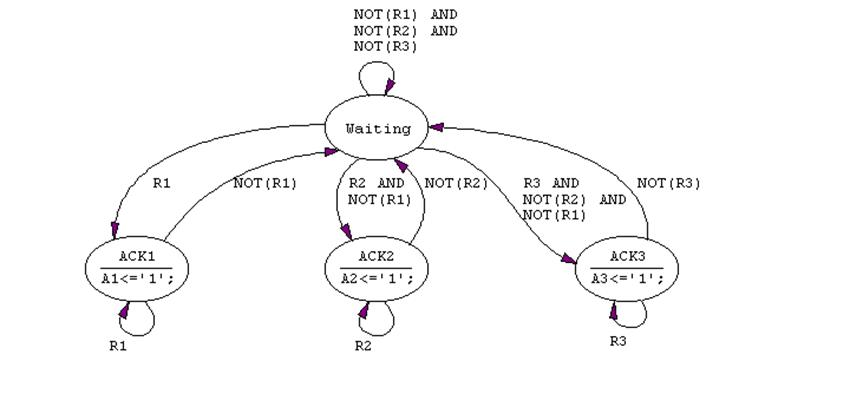

Диаграмма состояний представленная выше описывает арбитр ресурса, который распределяет ресурс, типа шины, в одной схеме одновременно. Арбитр имеет три основных входных сигнала с именами R1, R2, и R3, и три основных выходных сигнала с именами A1, A2, и A3. Входные сигналы - линии запроса, исходящие из отдаленной схемы, и выходные сигналы - линии подтверждения, возвращающиеся к той же самой отдаленной схеме.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity arbiter is

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.