architecture express of tri-state is

begin

output_signal <= input_signal when ena = '1' else 'Z' ;

end express ;

Обычно, одновременное назначение на один сигнал в VHDL не допустимо, так как это вызвало бы конфликты данных. Однако, если выражение ’Z‘ определено в каждом присвоении, то это одновременное назначение походит на множественные буферы с тремя состояниями, управляемые той же самой шиной.

entity THREE_STATE is

port ( D1,D2: in std_logic ;

EN1,EN2: in std_logic ;

Y: out std_logic) ;

end THREE_STATE ;

architecture BEHAVIOR of THREE_STATE is

begin

Y <= D1 when EN1 = '1' else 'Z' ;

Y <= D2 when EN2 = '1' else 'Z' ;

end BEHAVIOR ;

Инструментальные средства синтеза не проверяют конфликты шин при назначениях с тремя состояниями. Поэтому, убедитесь, что разрешающие сигналы задающего устройства с тремя состояниями никогда не активны одновременно. В этом примере, ena_1 и ena_2 не могут одновременно принимать значение '1'.

В этих примерах показано описание, для выходных портов (порты устройства). Порт также можно описать при помощи внутреннего сигнала, тогда создадутся внутренние шины. Если технология цели не поддерживает внутренние задающие устройства с тремя состояниями, логический синтез может преобразовать буферы с тремя состояниями в регулярную логику.

Массивы задающих устройств с тремя состояниями.

Чтобы создать массив задающих устройств с тремя состояниями, приведите пути ввода данных и выводы к типу std_logic_vector. Если разрешающий сигнал, является истинным, массив данных d передается, иначе находится в состоянии высокого сопротивления (Z), заданного по умолчанию.

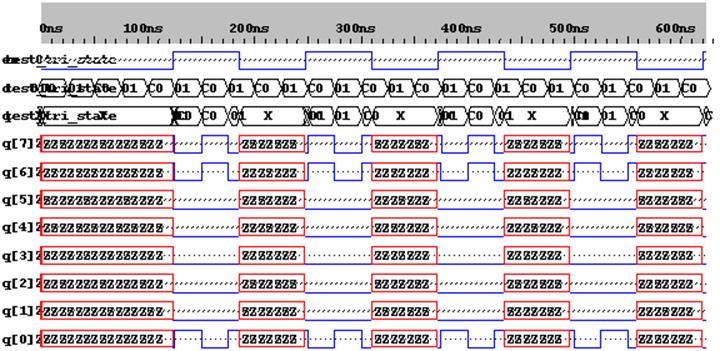

Ниже, вы можете видеть иллюстрацию моделирования массива с тремя состояниями.

|

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity tri_state is

port(d : in std_logic_vector(7 downto 0);

en : in std_logic;

q : inout std_logic_vector(7 downto 0));

end;

architecture behavior of tri_state is

begin

process (d, en)

begin

if en = '1' then

q <= d;

else

q <= (others=>'Z');

end if;

end process;

end;

Поскольку вся цифровая логика может быть выражена в терминах булевых уравнений, у вас имеется богатый набор операторов, включая И, ИЛИ, и НЕ, с помощью которых вы можете создавать любое произвольное выражение.

Альтернативой могут быть инструкции потока данных, для определения массива запускающих устройств с тремя состояниями, используя условное назначение сигнала.

entity THREE_STATE is

port ( D1,D2: in std_logic_vector(7 downto 0) ;

EN1,EN2: in std_logic ;

Y: out std_logic_vector(7 downto 0)) ;

end THREE_STATE ;

architecture BEHAVIOR of THREE_STATE is

begin

Y <= D1 when EN1 = '1' else "ZZZZZZZZ" ;

Y <= D2 when EN2 = '1' else "ZZZZZZZZ" ;

end BEHAVIOR ;

Этот код генерирует два набора из восьми буферов с тремя состояниями, два на каждой строке шины Y. Как в случае с единственным задающим устройством с тремя состояниями, шиной может быть внутренний сигнал, или порты.

Арифметика.

Диапазон целых чисел.

Лучше использовать целые с диапазоном, вместо “несвязанных” целых чисел. В VHDL, несвязанное целое число (целое число указанное без диапазона) гарантировано будет иметь диапазон от -2147483647 до +2147483647. Это означает, что по крайней мере необходимы 32 бита, чтобы описать принадлежность объекта этого типа. Инструментальные средства синтеза должны генерировать большое количество логики, чтобы исполнить операции над этими объектами. Часть этой логики может стать избыточной и устраниться в процессе оптимизации, но время выполнения значительно замедлится. Если вы используете целые числа как порты, перед алгоритмами синтеза встает сложная задача, поскольку вся логика работы не должна измениться. Поэтому, если вы не нуждаетесь в полном диапазоне целого числа, определите диапазон, который необходим для представления объекта:

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.