Если скомпилировать этот текст, вы можете создать триггер типа защелка с сигналом "a" как условным данным, сигналом "выбора", поскольку блокировка разрешает сигнал, и сигналом "y" как выхода «защелки». Вообще вместе с оператором if необходимо определить еще инструкцию else, если вы не подразумеваете «защелку» или триггер, как в следующих примерах:

if (clock'event and clock== 1)

or

if (rising_edge(clk) )

|

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

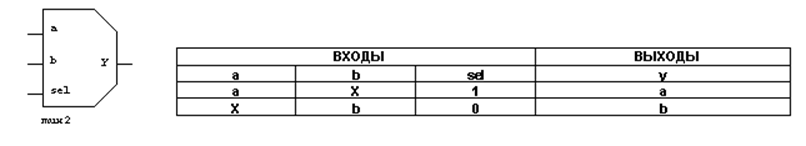

entity mux2 is

port (a, b, sel : in std_logic;

y : out std_logic);

end;

architecture behavior of mux2 is

begin

process (a,b,sel)

begin

if (sel = '0') then

y <= a;

else

y <= b;

end if;

end process;

end behavior;

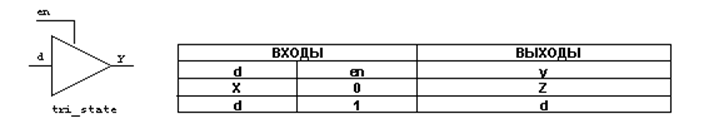

Буферы с тремя состояниями.

Этот раздел описывает то, как создать задающее устройство с тремя состояниями в VHDL. Большинство программируемых логических устройств, представляют из себя блоки ввода - вывода, которые используются задающими устройствами с тремя состояниями, для управления сигналами логической истины (1) или лжи (0), или состоянием высокого сопротивления (Z). Из-за разнообразия состояний сигнала модель должна использовать сигналы типа std_logic.

|

В примере ниже, описывается буфер с тремя состояниями.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity tri_state is

port(d, en : in std_logic;

q : inout std_logic);

end;

architecture behavior of tri_state is

begin

process (d, en)

begin

if en = '1' then

q <= d;

else

q <= 'Z';

end if;

end process;

end;

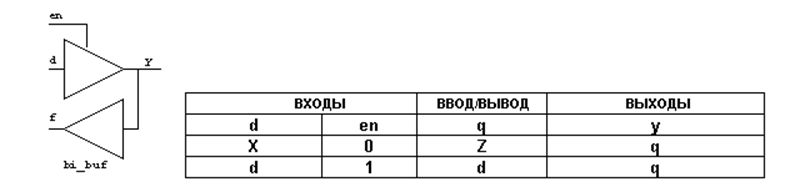

Большинство программируемых логических элементов представляют из себя ячейки ввода - вывода, которые могут быть запрограммированы, как реверсивные буферы. Основную модель с тремя состояниями можно изменить, так что разместится эта архитектура.

|

Реверсивный штырек, Y, используется как вход, когда задающее устройство с тремя состояниями заблокировано.

Ниже приведен пример кода описывающего реверсивный буфер.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity bi_buf is

port(d, en : in std_logic;

y : inout std_logic;

f : out std_logic);

end;

architecture behavior of bi_buf is

begin

process (d, en)

begin

if en = '1' then

y <= d;

else

y <= 'Z';

end if;

end process;

f <= y;

end;

Возможности отказаться от использования портов в режиме ввода-вывода. Порт в режиме ввода-вывода в проекте на VHDL должен использоваться очень осторожно. Его использование обычно ограничивается в моделях двунаправленных буферов, которые облегчают использование общего порта для ввода и вывода.

В инструкциях потока данных, буфер с тремя состояниями может быть создан при помощи условного оператора.

architecture BEHAVIOR of THREE_STATE is

begin

Y <= D when EN = '1' else 'Z' ;

end BEHAVIOR ;

D и условие EN = ’1‘ могут быть полными выражениями. При логическом синтезе генерируется комбинационная логика, управляющая входом или разрешением буфера с тремя состояниями для этих выражений.

Заблокированный буфер с тремя состояниями будет находиться в состоянии высокого сопротивления. Сам VHDL не предопределяет состояние высокого сопротивления, но IEEE, 1164 (стандарт для логических пакетов) определяет символ 'Z', для описания поведения, которое точно походит на поведение буфера с тремя состояниями с высоким сопротивлением. Сигнал (порта или внутренний сигнал) стандартного логического типа может иметь значение 'Z'. Инструментальные средства синтеза распознают 'Z' и создают буфер с тремя состояниями в соответствии с условным назначением сигнала 'Z':

entity tri-state is

port ( input_signal : in std_logic ;

ena : in std_logic ;

output_signal : out std_logic

) ;

end tri-state ;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.