Федеральное агентство по образованию РФ

Рязанский государственный радиотехнический университет

Кафедра САПР вычислительных средств

Моделирование цифровых устройств с использованием пакета VHDL.

Пояснительная записка

к курсовой работе по дисциплине

“Схемотехника электронных средств”

Выполнила: ст. гр. 346

Проверил:

Рязань 2006.

Содержание

Задание 3

Введение 4

Описание задания 5

Моделирование элементов

1.Схема К559ИП2П 7

2.Схема К589АП16 8

3.Схема К155ЛН1 10

4.Схема К155ЛА2 11

5.Схема К155ТЛ3 12

6.Схема К155ТМ7 13

7.Схема К155ЛА4 14

8.Схема К155ИД4 15

9.Схема К155ЛИ1 17

10.Схема К559ИП1П 18

Моделирование схемы УПП-8 19

Заключение 20

Список литературы 21

Приложение 1 22

Приложение 2 29

Рязанский государственный радиотехнический университет

Кафедра САПР ВС

Тема: Моделирование цифровых устройств с использованием пакета VHDL

Срок представления к защите:_____________________ 2006г.

Задание выдано:__________________________________ 2006г.

Задание принято к исполнению______ /студент гр.346 /

Задание выдал _____________________ /асс. каф. САПР ВС /

Введение

Широкое распространение цифровой техники, ее доступность обывателю и дешевизна обусловлены появлением интегральных микросхем. Цифровые устройства, собранные на базе дискретных транзисторов и диодов, имели значительные габаритные размеры и массу; обладали невысокой надежностью в связи с наличием большого числа элементов и паяных связей между ними. Интегральные микросхемы, содержащие в своем составе десятки и сотни тысяч компонентов, позволили по-новому подойти к проектированию и изготовлению цифровых устройств.

В процессе усовершенствования интегральных технологий стало возможным создание сложнейших устройств, надежных и обладающих малыми габаритами и высоким быстродействием.

Традиционный подход к проектированию дискретных вычислительных систем (ДС) состоит в последовательном решении задач анализа и оптимизации некоторого начального варианта проектируемой ДС. Поэтому давней мечтой разработчиков ДС было создание единых средств описания ДС, которые позволяли бы решать задачи верификации и синтеза схем с различной степенью детальности их описания и, таким образом, объединять этапы проектирования в единый процесс нисходящего проектирования "сверху вниз". Появление языка VHDL в определенной степени позволяет автоматизировать задачи проектирования от описания алгоритма функционирования ДС до реализации кристаллов микросхем. При этом понятие синтез следует определить как формализованный процесс построения схемы из некоторого заданного набора компонентов.

Описание задания

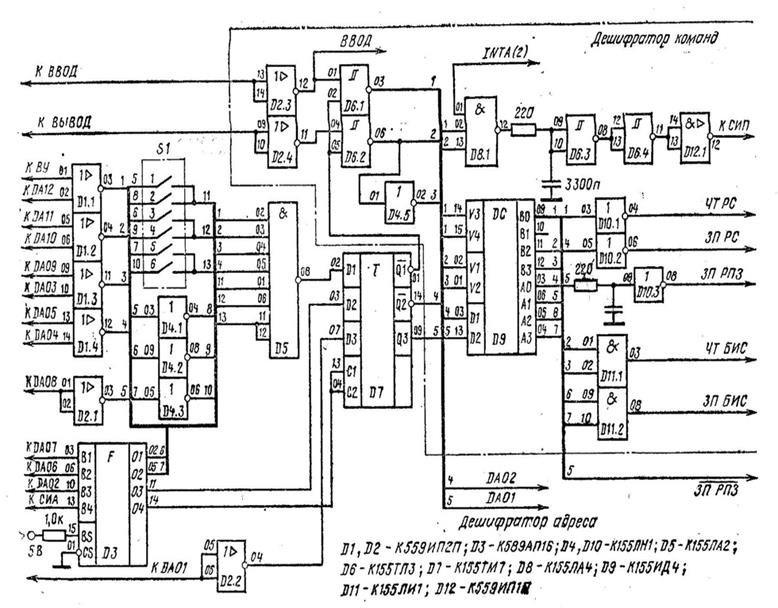

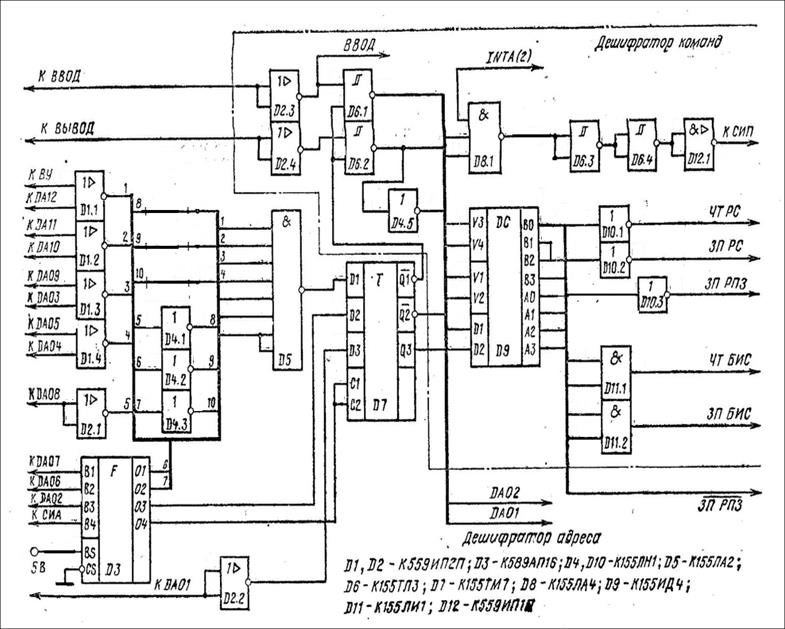

На языке VHDLнужно описать схему дешифратора адреса (ДА) и дешифратора команд (ДК) УПП-8. Схема ДА и ДК представлена на рис.1 ниже:

Рис.1

Схема дешифратора адреса и дешифратора команд УУП-8.

Для осуществления моделирования данной схемы в среде VHDL адаптируем ее и пронумеруем все связи (рис.2).

|

|||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||

|

|

||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||

|

|

||||||||||||||||||||||||||||

|

|

||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||

Рис.2

Моделирование элементов

1.Схема К559ИП2П

Представляет собой элемент, реализующий логическую функцию ИЛИ-НЕ

с временем задержки на выходе равной 20 нс. Данная схема реализует

логическую функцию: ![]()

Таблица истинности №1

Таблица истинности №1

|

Х1 |

Х2 |

У |

|

0 |

0 |

1 |

|

1 |

0 |

0 |

|

0 |

1 |

0 |

|

1 |

1 |

0 |

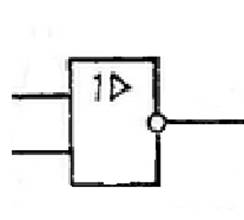

Рис.3

Условное графическое изображение К559ИП2П

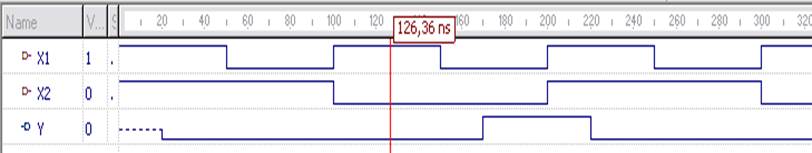

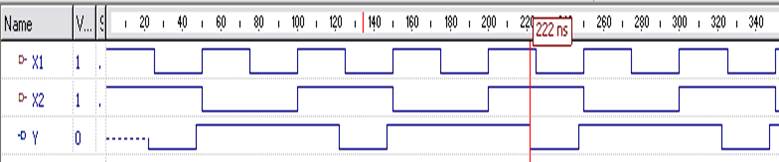

Временная диаграмма схемы представлена на рис.4

Рис.4

2.Схема К589АП16

Микросхема К589АП16 – шинный формирователь, является параллельным двунаправленным формирователем сигналов для управления шинами в цифровых вычислительных устройствах и представляет собой 4-канальный коммутатор, имеющий в каждом канале одну шину только для приема информации, одну шину только для выдачи информации и одну двунаправленную шину для приема и выдачи информации. В шинном формирователе информация проходит без изменения. Условное графическое обозначение К589АП16 представлено на рис.5

|

Рис.5

Таблица №2

|

Состояние входов |

Направление передачи информации |

Выходы в состояние «выключено» |

|

|

CS |

BS |

||

|

0 |

0 |

От входов DI0-D13 до выходов B1-B4 |

O1-O4 |

|

0 |

1 |

От входов B1-B4 до выходов O1-O4 |

B1-B4 |

|

1 |

1 |

Передача отсутствует |

O1-O4, B1-B4 |

Смоделируем схему К589АП16 для 2 и 3 случаев, т.к они более наглядно описывают работу элемента в схеме при условие, что время задержки для второго случая составляет 15нс.

|

Состояние входов |

Направление передачи информации |

Выходы в состояние «выключено» |

|

|

CS |

BS |

||

|

0 |

0 |

От входов DI0-D13 до выходов B1-B4 |

O1-O4 |

|

0 |

1 |

От входов B1-B4 до выходов O1-O4 |

B1-B4 |

|

1 |

1 |

Передача отсутствует |

O1-O4, B1-B4 |

Таблица истинности №3

|

CS |

O1 |

O2 |

O3 |

O4 |

|

1 |

U |

U |

U |

U |

|

0 |

B1 |

B2 |

B3 |

B4 |

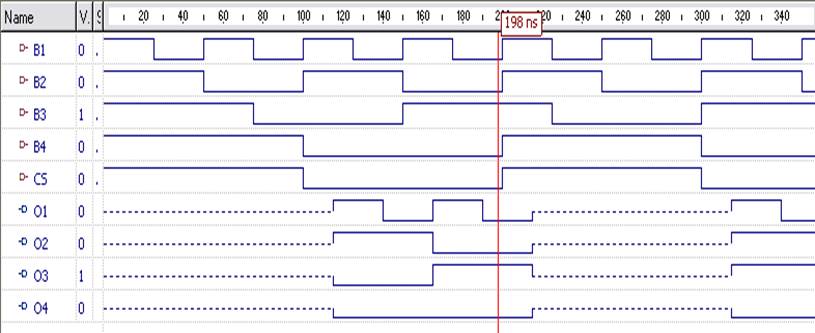

Временная диаграмма схемы представлена на рис.6

Рис.6

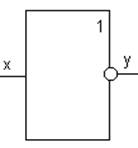

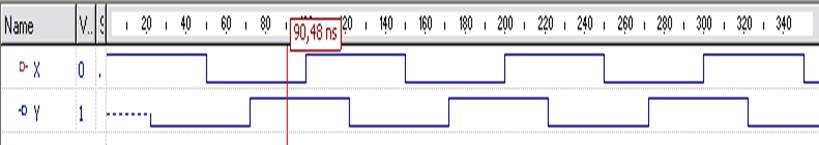

3.Схема К155ЛН1

Представляет собой логический элемент серии ТТЛ, выполняющий логическую функцию НЕ, с временем задержки на выходе равной 22нс.

Условное графическое изображение схемы представлено на рис.7.

Рис.7

Данная схема

реализует логическую функцию: ![]()

Таблица истинности № 4

|

X |

Y |

|

0 |

1 |

|

1 |

0 |

Временная диаграмма схемы представлена на рис.8

Рис.8

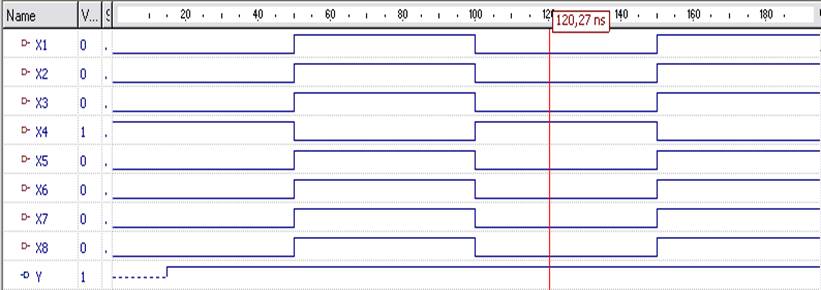

4.Схема К155ЛА2

Представляет собой логический элемент серии ТТЛ, выполняющий логическую функцию 8И-НЕ, с временем задержки 15нс.

Условное графическое изображение схемы представлено на рис.9

|

|

|

|

|

|

|

|

|

Рис.9

Данная схема

реализует логическую функцию: ![]()

Таблица истинности №5

|

Х1 |

Х2 |

Х3 |

Х4 |

Х5 |

Х6 |

Х7 |

Х8 |

У |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

|

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

… |

… |

… |

… |

… |

… |

… |

… |

… |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

Временная диаграмма схемы представлена на рис.10

Рис.10

5.Схема К155ТЛ3

Представляет собой логический элемент со свойствами триггера Шмидта, реализующий логическую функцию 2И-НЕс временем задержки – 22нс. Имеет внутреннюю положительную обратную связь, глубина которой подобрана так, чтобы получить передаточную характеристику со значительным гистерезисом. Выходной сигнал логического элемента Шмидта имеет крутые импульсные перепады, длительность которых не зависит от скорости нарастания или спада входного сигнала.

Микросхема К155ТЛ3 имеет четыре двухвходовых элемента 2И-НЕ.

Условное графическое изображение схемы представлено на рис.11

|

|||||

Рис.11

Временная диаграмма схемы представлена на рис.12

Рис.12

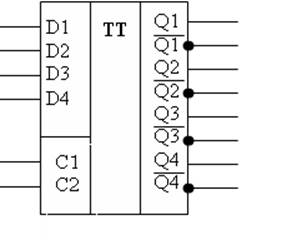

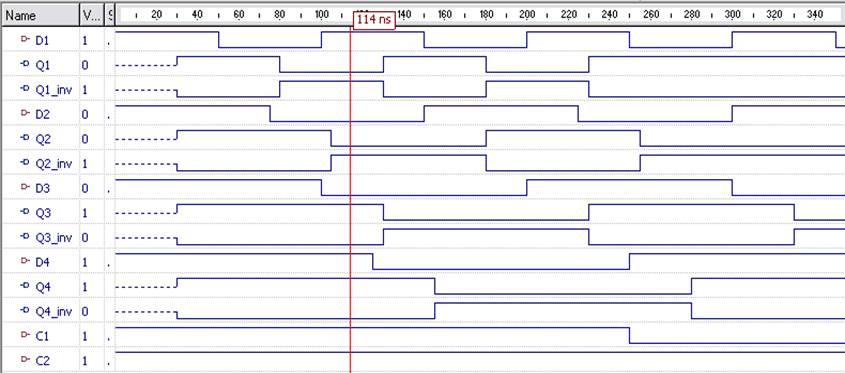

6.Схема К155ТМ7

Представляет собой триггер типа D, содержит две пары D-триггеров. Пары представляют собой простейшие защелки данных по 2 бита. Каждая пара триггера имеет вход разрешения загрузки. Когда на такой вход разрешения подается напряжение высокого уровня, данные присутствующие на входах D, без изменения отображаются на выходе Q.

Условное графическое изображение схемы представлено на рис.13

Рис.13

Таблица состояния триггера (Таб.№6)

|

Режим работы |

Вход |

Выход |

||

|

С |

D |

Q |

|

|

|

Разрешение передачи данных на вход |

1 |

0,1 |

0,1 |

1,0 |

|

Защелкивание данных |

0 |

х |

q |

|

Время задержки составляет 30нс.

Временная диаграмма схемы представлена на рис.14

Рис.14

7.Схема К155ЛА4

Представляет собой логический элемент серии ТТЛ, выполняющий

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.