Министерство образования Российской Федерации

Рязанская государственная радиотехническая академия

Кафедра САПР вычислительных средств

Пояснительная записка

к курсовой работе

по дисциплине

“Схемотехника электронных средств”

Выполнил ст-т гр. 145

Проверил:

Рязань, 2003

Содержание

1.Задание 3

2.Описание задания 4

3.Описание элементов 5

3.1. Микросхема К155ЛА3 5

3.2. Микросхема К155ИЕ5 6

3.3. Микросхема К155ТМ2 8

3.4. Микросхема К155ИД4 10

3.5. Микросхема К589ИР12 12

4.Листинг программы 14

4.1.Файл N_AND.vhd 14

4.2.Файл IC_k155ie5.vhd 15

4.3.Файл IC_k155tm2.VHD 16

4.4.Файл IC_k155id4.vhd 17

4.5.Файл IC_k589ir12.vhd 18

4.6.Файл Top.vhd 19

5.WaveForm схемы 24

Список литературы 25

Данная схема представляет собой помехоустойчивый АЦП, сопрягаемый с микропроцессором КР580ИК80. Сопряжение выполняется с помощью портов ввода на основе программируемого параллельного интерфейса или многорежимных буферных регистров. Данный 12-разрядный АЦП работает по принципу двухтактного интегрирования с цифровой коррекцией дрейфа нуля и крутизны преобразования. Схема сопряжения с системной шиной реализована на основе многорежимных буферных регистров К582ИР12.

Представляет собой 4 логических элемента 2И-НЕ. Содержит 56 интегральных элементов. Масса не более 1 г.

Рис.2. Условное графическое обозначение К155ЛА3

Назначение выводов

|

Вывод |

Назначение |

Вывод |

Назначение |

|

|

1 |

Вход X1 |

8 |

Выход Y3 |

|

|

2 |

Вход X2 |

9 |

Вход X5 |

|

|

3 |

Выход Y1 |

10 |

Вход X6 |

|

|

4 |

Вход X3 |

11 |

Выход Y4 |

|

|

5 |

Вход X4 |

12 |

Вход X7 |

|

|

6 |

Выход Y2 |

13 |

Вход X8 |

|

|

7 |

Общий |

14 |

Напряжение питания |

Время задержки распространения 15 нс.

Таблица истинности

|

Вход 1 |

Вход 2 |

Выход |

|

0 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

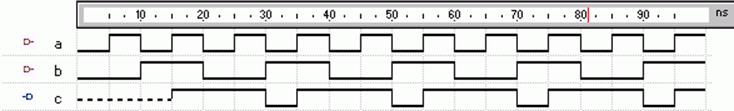

Рис.3. WaveForm логического элемента 2И-НЕ

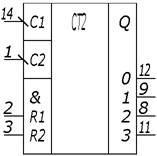

Микросхема представляет собой четырехразрядный двоичный асинхронный счетчик. Микросхема счетчика состоит из четырёх JK-триггеров, которые соединены соответствующим образом (Рис.5) для образования счетчика делителя на 2 и 8.

Рис.4. Условное графическое обозначение К155ИЕ5

Рис.5. Функциональная схема К155ИЕ5

Назначение выводов

|

Вывод |

Назначение |

Вывод |

Назначение |

|

|

1 |

Вход счетный С2 |

8 |

Выход Q3 |

|

|

2 |

Вход установки в 0 R0(1) |

9 |

Выход Q2 |

|

|

3 |

Вход установки в 0 R0(2) |

10 |

Общий |

|

|

4 |

Свободный |

11 |

Выход Q4 |

|

|

5 |

Напряжение питания |

12 |

Выход Q1 |

|

|

6 |

Свободный |

13 |

Свободный |

|

|

7 |

Свободный |

14 |

Вход счетный С1 |

Время задержки распространения 135 нс.

У счетчика имеются лишь входы сброса в нуль. Счетчик работает по заднему фронту положительного входного сигнала. Выделены две части: один триггер (одноразрядный счетчик) со входом С1 и выходом 1 и три триггера (трехразрядный счетчик) со входом С2 и выходами 2, 4, 8. Оба счетчика двоичные, то есть первый считает до двух, а второй — до 8. При объединении входа С2 с выходом 1 получается 4-разрядный двоичный счетчик, считающий до 16. Счет производится по отрицательному фронту входного сигнала. Предусмотрена возможность сброса в нуль по сигналам R1 и R2, объединенных функцией И.

Таблица истинности счетчика ИЕ5 присоединении входа С2 и выхода 1 (при 4-разрядном выходном коде):

|

Входы |

Выходы |

|||||

|

С1 |

R1 |

R2 |

8 |

4 |

2 |

1 |

|

Х |

1 |

1 |

0 |

0 |

0 |

0 |

|

1→0 |

0 |

Х |

Счет |

|||

|

1→0 |

Х |

0 |

Счет |

|||

Счет производится согласно следующей таблице:

|

Счет |

Выход |

|||

|

8 |

4 |

2 |

1 |

|

|

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

|

2 |

0 |

0 |

1 |

0 |

|

3 |

0 |

0 |

1 |

1 |

|

4 |

0 |

1 |

0 |

0 |

|

5 |

0 |

1 |

0 |

1 |

|

6 |

0 |

1 |

1 |

0 |

|

7 |

0 |

1 |

1 |

1 |

|

8 |

1 |

0 |

0 |

0 |

|

9 |

1 |

0 |

0 |

1 |

|

10 |

1 |

0 |

1 |

0 |

|

11 |

1 |

0 |

1 |

1 |

|

12 |

1 |

1 |

0 |

0 |

|

13 |

1 |

1 |

0 |

1 |

|

14 |

1 |

1 |

1 |

0 |

|

15 |

1 |

1 |

1 |

1 |

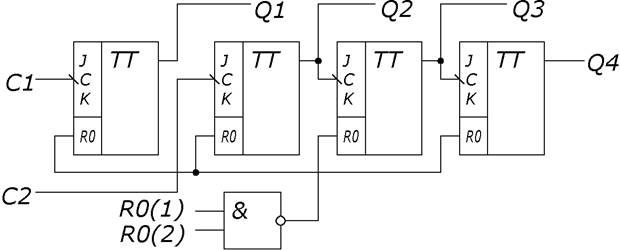

Рис.6. WaveForm К155ИЕ5

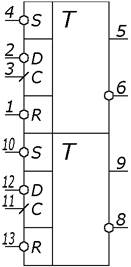

Микросхема представляет собой 2 D-триггера с прямым и инверсным выходами. Триггер имеет вход установки S и вход сброса R, помимо них он имеет один информационный вход D (вход данных) и один тактовый вход C. Содержит 70 интегральных элементов. Масса не более 1 г.

Рис.7. Условное графическое обозначение К155ТМ2

Назначение выводов

|

Вывод |

Назначение |

Вывод |

Назначение |

|

|

1 |

Инверсный вход установ- ки 0 R1 |

8 |

Инверсный выход Q2 |

|

|

2 |

Вход D1 |

9 |

Выход Q2 |

|

|

3 |

Вход синхронизации С1 |

10 |

Инверсный вход установ- ки 1 S2 |

|

|

4 |

Инверсный вход установ- ки 1 S1 |

11 |

Вход синхронизации С2 |

|

|

5 |

Выход Q1 |

12 |

Вход D2 |

|

|

6 |

Инверсный выход Q1 |

13 |

Инверсный вход установ- ки 0 R2 |

|

|

7 |

Общий |

14 |

Напряжение питания |

Время задержки распространения 40 нс.

Таблица истинности D-триггера ТМ2

|

Входы |

Выходы |

||||

|

S |

R |

C |

D |

Q |

-Q |

|

0 |

1 |

X |

X |

1 |

0 |

|

1 |

0 |

X |

X |

0 |

1 |

|

0 |

0 |

X |

X |

Не определено |

|

|

1 |

1 |

0→1 |

1 |

1 |

0 |

|

1 |

1 |

0→1 |

0 |

0 |

1 |

|

1 |

1 |

0 |

X |

Не меняется |

|

|

1 |

1 |

1 |

X |

Не меняется |

|

|

1 |

1 |

1→0 |

X |

Не меняется |

|

Тактуется триггер (то есть изменяет свое состояние) по положительному фрогту сигнала С (по его переходу из нуля в единицу) в зависимости от состояния входа данных D. Если на входе D единичный сигнал, то по фронту сигнала С прямой выход триггера устанавливается в единицу (инверсный — в нуль). Если же на входе D нулевой сигнал, то по фронту сигнала С прямой выход триггера устанавливается в нуль (инверсный — в единицу).

Рис.8. WaveForm К155ТМ2

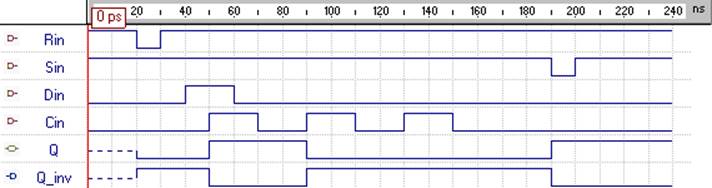

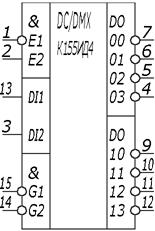

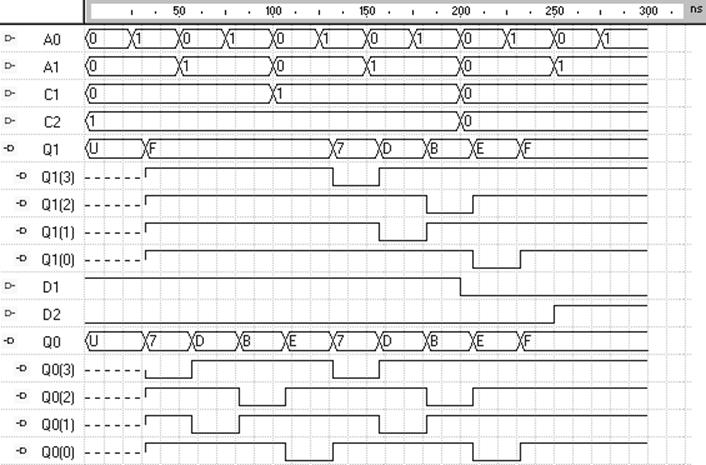

Микросхема представляет собой 2 дешифратора, принимающих двухразрядный код адреса А0, А1.

Рис.9. Условное графическое обозначение К155ИД4

Назначение выводов

|

Вывод |

Назначение |

Вывод |

Назначение |

|

|

1 |

Инверсный вход разрешения Е1 |

9 |

Выход |

|

|

2 |

Вход разрешения Е2 |

10 |

Выход |

|

|

3 |

Адресный вход А0 |

11 |

Выход |

|

|

4 |

Выход |

12 |

Выход |

|

|

5 |

Выход |

13 |

Адресный вход А1 |

|

|

6 |

Выход |

14 |

Инверсный вход разрешения G2 |

|

|

7 |

Выход |

15 |

Инверсный вход разрешения G1 |

|

|

8 |

Общий |

16 |

Напряжение питания |

Рис.10. WaveForm К155ИД4

Таблица истинности:

|

А0 |

А1 |

ЕА |

-ЕА |

Y1 |

Y2 |

Y3 |

Y4 |

|

X |

X |

1 |

X |

1 |

1 |

1 |

1 |

|

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

|

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

|

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

|

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

|

1 |

X |

X |

0 |

1 |

1 |

1 |

1 |

Микросхема представляет собой многорежимный буферный регистр. Имеет встроенную логическую схему и независимый триггер для формирования запроса на прерывание центрального процессора.

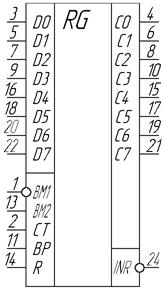

Рис.11. Условное графическое обозначение К589ИР12

Назначение выводов

|

Вывод |

Назначение |

Вывод |

Назначение |

|

|

1 |

Выбор кристалла |

13 |

Выбор кристалла |

|

|

2 |

Выбор режима |

14 |

Установка нуля |

|

|

3 |

Информационный вход |

15 |

Выход |

|

|

4 |

Выход |

16 |

Информационный вход |

|

|

5 |

Информационный вход |

17 |

Выход |

|

|

6 |

Выход |

18 |

Информационный вход |

|

|

7 |

Информационный вход |

19 |

Выход |

|

|

8 |

Выход |

20 |

Информационный вход |

|

|

9 |

Информационный вход |

21 |

Выход |

|

|

10 |

Выход |

22 |

Информационный вход |

|

|

11 |

Стробирующий сигнал |

23 |

Запрос прерывания |

|

|

12 |

Общий |

24 |

Напряжение питания |

Время задержки распространения 30 нс.

Принцип работы.

Информационные D-триггерыповторяют

входную информацию при ![]() или

CT=1, а также при BP=1 и CT=0. При BP=0 и

или

CT=1, а также при BP=1 и CT=0. При BP=0 и ![]() при CT=0 происходит хранение входной информации. При CT=1 или

при CT=0 происходит хранение входной информации. При CT=1 или

![]() выходные буферные

каскады разблокированы и данные поступают на выход соответствующей линии

выходных данных. При R=0 данные регистра обнуляются.

выходные буферные

каскады разблокированы и данные поступают на выход соответствующей линии

выходных данных. При R=0 данные регистра обнуляются.

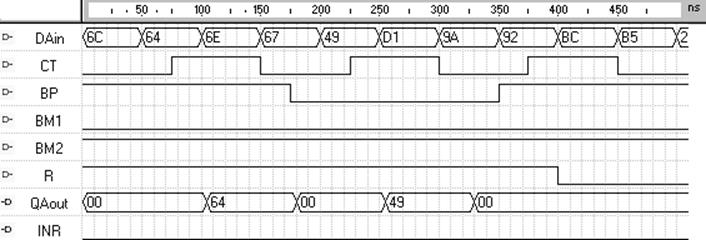

Рис.12. WavwForm К589ИР12

-------------------------------------------------------------------

-- File: ..\SRC\N_AND.VHD

-------------------------------------------------------------------

library IEEE;

use IEEE.std_logic_1164.all;

entity N_AND is

port

(

a: in STD_LOGIC;

b: in STD_LOGIC;

c: out STD_LOGIC

);

end N_AND;

architecture N_AND of N_AND is

begin

c <= transport (a nand b) after 15 ns;

end N_AND;

-------------------------------------------------------------------

-- File: ..\SRC\IC_k155ie5.vhd

-------------------------------------------------------------------

library IEEE;

use IEEE.std_logic_1164.all;

library SYNOPSYS;

use SYNOPSYS.std_logic_arith.all;

use SYNOPSYS.std_logic_unsigned.all;

entity IC_k155ie5 is

port

(

CLK: in STD_LOGIC;

RESET: in STD_LOGIC;

Q: out STD_LOGIC_VECTOR (3 downto 0)

);

end IC_k155ie5;

architecture IC_k155ie5 of IC_k155ie5 is

begin

process (CLK, RESET)

variable Qint: STD_LOGIC_VECTOR (3 downto 0);

begin

if RESET='1' then

Qint := "0000";

else

if CLK'event and CLK='1' then

if Qint<15 then

Qint:=Qint+1;

else

Qint:="0000";

end if;

end if;

end if;

Q <= transport Qint after 135 ns;

end process;

end IC_k155ie5;

-------------------------------------------------------------------

-- File: ..\SRC\IC_k155tm2.VHD

-------------------------------------------------------------------

library IEEE;

use IEEE.std_logic_1164.all;

library SYNOPSYS;

use SYNOPSYS.std_logic_arith.all;

use SYNOPSYS.std_logic_unsigned.all;

entity IC_k155tm2 is

port

(

Sin: in STD_LOGIC;

Din: in STD_LOGIC;

Cin: in STD_LOGIC;

Rin: in STD_LOGIC;

Q: inout STD_LOGIC;

Q_inv: out STD_LOGIC

);

end IC_k155tm2;

architecture IC_k155tm2 of IC_k155tm2 is

signal Qt:STD_LOGIC;

begin

process (Rin, Sin, Cin)

begin

Qt<= Q;

if (Rin='0' and Sin='1') then Qt <= '0';

elsif (Rin='1' and Sin='0') then Qt <= '1';

elsif (Rin='1' and Sin='1') then

if(Cin'event and Cin='1') then

if(Din='1')

then Qt <= '1';

else Qt <= '0';

end if;

end if;

else

assert not (Sin='0' and Rin='0')

report "одновременный 0 на S и R входе D-триггера"

severity warning;

end if;

Q <= transport Qt after 40 ns;

Q_inv <= transport not Qt after 40 ns;

end process;

end IC_k155tm2;

-------------------------------------------------------------------

-- File: ..\SRC\IC_k155id4.vhd

-------------------------------------------------------------------

library IEEE;

use IEEE.std_logic_1164.all;

library SYNOPSYS;

use SYNOPSYS.std_logic_arith.all;

use SYNOPSYS.std_logic_unsigned.all;

entity IC_k155id4 is

port

(

A0: in STD_LOGIC;

A1: in STD_LOGIC;

D1: in STD_LOGIC;

D2: in STD_LOGIC;

C1: in STD_LOGIC;

C2: in STD_LOGIC;

Q0: out STD_LOGIC_VECTOR (3 downto 0);

Q1: out STD_LOGIC_VECTOR (3 downto 0)

);

end IC_k155id4;

architecture IC_k155id4 of IC_k155id4 is

signal Qres0:STD_LOGIC_VECTOR (3 downto 0);

signal Qres1:STD_LOGIC_VECTOR (3 downto 0);

begin

Qres0 <=

"0111" when (A0 & A1 & D2 & D1)="0001" else

"1011" when (A0 & A1 & D2 & D1)="0101" else

"1101" when (A0 & A1 & D2 & D1)="1001" else

"1110" when (A0 & A1 & D2 & D1)="1101" else

"1111";

Qres1 <=

"0111" when (A0 & A1 & C1 & C2)="0011" else

"1011" when (A0 & A1 & C1 & C2)="0111" else

"1101" when (A0 & A1 & C1 & C2)="1011" else

"1110" when (A0 & A1 & C1 & C2)="1111" else

"1111";

Q0 <= transport Qres0 after 32 ns;

Q1 <= transport Qres1 after 32 ns;

end IC_k155id4;

-------------------------------------------------------------------

-- File: ..\SRC\IC_k155ir12.vhd

-------------------------------------------------------------------

library IEEE;

use IEEE.std_logic_1164.all;

library SYNOPSYS;

use SYNOPSYS.std_logic_arith.all;

use SYNOPSYS.std_logic_unsigned.all;

entity IC_k589ir12 is

port

(

DAin: in STD_LOGIC_VECTOR(7 downto 0);

R: in STD_LOGIC;

BM1: in STD_LOGIC;

BM2: in STD_LOGIC;

CT: in STD_LOGIC;

BP: in STD_LOGIC;

QAout:out STD_LOGIC_VECTOR(7 downto 0):="00000000";

INR: out STD_LOGIC:='0'

);

end IC_k589ir12;

architecture IC_k589ir12 of IC_k589ir12 is

signal Regist:STD_LOGIC_VECTOR(7 downto 0):="00000000";

begin

process(R, BM1, BM2, CT, BP)

begin

if R'event and R='0'then

QAout <= "00000000";

else

if (CT and not BM1 and BM2) ='1' then

QAout <= transport DAin after 30 ns;

else

QAout <= transport "00000000" after 30 ns;

end if;

end if;

end process;

end IC_k589ir12;

-------------------------------------------------------------------

-- File: ..\SRC\Top.VHD

-------------------------------------------------------------------

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity Top is

port

(

In1: inout STD_LOGIC;

In2: inout STD_LOGIC;

A0: in STD_LOGIC;

A1: in STD_LOGIC;

OBB: in STD_LOGIC;

Read: in STD_LOGIC;

Write: in STD_LOGIC;

At: out STD_LOGIC;

Ct: out STD_LOGIC;

Dt: out STD_LOGIC;

TPR: out STD_LOGIC;

D: out STD_LOGIC_VECTOR (11 downto 0)

);

end Top;

architecture Structure of Top is

component N_AND is

port

(

a: in STD_LOGIC;

b: in STD_LOGIC;

c: out STD_LOGIC

);

end component;

component k155ie5 is

port

(

CLK: in STD_LOGIC;

RESET: in STD_LOGIC;

Q: out STD_LOGIC_VECTOR (3 downto 0)

);

end component;

component k155tm2 is

port

(

Sin: in STD_LOGIC;

Din: in STD_LOGIC;

Cin: in STD_LOGIC;

Rin: in STD_LOGIC;

Q: inout STD_LOGIC;

Q_inv: out STD_LOGIC

);

end component;

component k589ir12 is

port

(

DAin: in STD_LOGIC_VECTOR(7 downto 0);

R: in STD_LOGIC;

BM1: in STD_LOGIC;

BM2: in STD_LOGIC;

CT: in STD_LOGIC;

BP: in STD_LOGIC;

QAout:out STD_LOGIC_VECTOR(7 downto 0);

INR: out STD_LOGIC

);

end component;

component k155id4 is

port

(

A0: in STD_LOGIC;

A1: in STD_LOGIC;

D1: in STD_LOGIC;

D2: in STD_LOGIC;

C1: in STD_LOGIC;

C2: in STD_LOGIC;

Q0: out STD_LOGIC_VECTOR (3 downto 0);

Q1: out STD_LOGIC_VECTOR (3 downto 0)

);

end component;

signal a_bus:STD_LOGIC_VECTOR (16 downto 1);

signal s1, s2, s3, s4, s5, s6, s7, s8, s9, s10,

s11, s12, s13, s14, s15:STD_LOGIC;

signal grn, one:STD_LOGIC;

signal s12_out, s18_Q0_out, s18_Q1_out:STD_LOGIC_VECTOR(3 downto

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.