Определение

принципов физической реализации преобразователей является важной частью 4-го

этапа процедуры их проектирования (см. рис. 1.3), так как его успешное

проведение влияет на характеристику затрат ![]() ,

а также на временные характеристики работы ПЛИС, на основе которой строится

ПФИ.

,

а также на временные характеристики работы ПЛИС, на основе которой строится

ПФИ.

Следует выделить, что при реализации на ПЛИС полученных ранее логических схем нейроузлов (как элементарных, однородных составляющих ИНС-преобразователей) возможны 3 основных способа их описания: схемотехнический редактор, языки описания аппаратуры (HDL, HardwareDescriptionLanguages), редактор состояний. Редактор состояний предназначен для программирования конечных автоматов. Как правило, он используется совместно со схемотехническим редактором либо с языковым описанием.

При вводе схемы с помощью схемотехнического редактора система автоматизированного проектирования не производит оптимизации введенной схемы, а только осуществляет трансляцию компонентов пользователя в элементы физической структуры ПЛИС.

При реализации языковых описаний система проектирования осуществляет определенную оптимизацию компонентов пользователя с задаваемыми параметрами. Поскольку таблицы преобразования (Look Up Table, LUT) современных ПЛИС эффективно реализуют функции 3-5 логических переменных, то для построения схем с повышенным быстродействием и низкими аппаратными затратами целесообразно минимизировать логические функции, содержащие более 5…6 переменных, например с помощью карт Карно. Вместе с тем следует сказать, что представление преобразователя в нейросетевом базисе через совокупности операций, выполняемых однородными нейронами (обычно с числом входов не более 3‑х) исключает применение этих карт, обеспечивая эффективную работу LUT‑таблиц.

Процесс программирования ПЛИС на реализацию ПФИ с помощью VHDL обычно описывают в виде 6 основных этапов.

1. Определение требований проектирования.

2. Описания проекта на VHDL или в схемотехническом редакторе (выбор метода проектирования и кодирование).

3. Моделирование исходного кода.

4. Синтез, оптимизация, размещение и трассировка проекта.

5. Моделирование после размещения.

6. Программирование прибора.

Аппаратные затраты на физическую реализацию преобразователя на ПЛИС рассчитаны через сумму отдельных затрат на ее компоненты:

![]() , (3.14)

, (3.14)

где ![]() ,

, ![]() ,

, ![]() и

и

![]() – затраты на реализацию всех таблиц

преобразования, всех триггеров, всей накристальной блочной памяти и всех

аппаратных умножитей соответственно.

– затраты на реализацию всех таблиц

преобразования, всех триггеров, всей накристальной блочной памяти и всех

аппаратных умножитей соответственно.

При этом на составляющие (3.14) накладывают следующие ограничения:

![]() ,

,

![]() ,

, ![]() и

и

![]() ,

,

где ![]() ,

,

![]() ,

, ![]() и

и

![]() .

.

В целом описание нейроструктур ПФИ на языке VHDL отличается простотой программ и малой емкостью памяти, затрачиваемой на хранение кодов. Поэтому в памяти могут храниться десятки тысяч описаний нейронов ПФИ, подключаемых к схеме по мере необходимости, например в случае построения системы с адаптацией к виду изменения входного сигнала и функционального преобразования.

Компактность описаний

операций преобразования "аналог → код" иллюстрируется приводимым

фрагментом программы на языке VHDL, описывающей нейроузел ![]() (

(![]() ) для ПФИ

) для ПФИ ![]() (см.

рис. 1.10,б):

(см.

рис. 1.10,б):

entityneurois // Подпрограмма для нейроузла

Port // Описание входов-выходов нейроузла

(f0 : instd_logic;

reset : in std_logic;

e_in : in std_logic;

tau : in std_logic;

a : out std_logic;

e : out std_logic);

end neuro;

architecture Behavioral of neuro is

signal u : std_logic; // Описаниевнутр. сигналаНУ

a_in : std_logic;

begin // Описание функционирования нейроузла

a <= a_in;

process(e_in, tau)

begin // Описаниекомбинационнойсхемы

u <= (tau and e_in) or a_in;

e <= e_in and a_in;

end process;

process(f0)

begin // Описаниеэлементовпамяти

if (f0=’1’ and f0’event) then

if (reset = ‘1’)

then a_in <= ‘0’;

else a_in <= u;

end if;

end if;

end process;

end Behavioral;

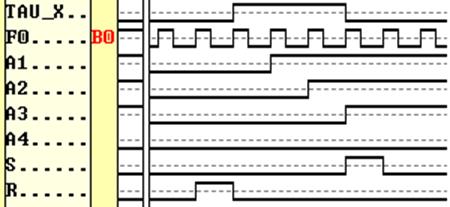

Экспериментальная

проверка работоспособности ИНС‑преобразователей, построенных на базе ПЛИС,

сводится к их верификации путем моделирования ее разработанной схемы средствами

САПР. Пример функционально-логического моделирования преобразователей в

приложении LogicSimulator пакета САПР XilinxFoundation для ПФИ ![]() показан

на рис. 3.4.

показан

на рис. 3.4.

Рис. 3.4.

Временные диаграммы работы ПФИ ![]() (см.

рис. 1.10,б) при формировании унитарного кода

(см.

рис. 1.10,б) при формировании унитарного кода ![]()

3.2.2. Особенности оценки технико-экономических характеристик нейропреобразователей на ПЛИС

Современные ПЛИС

характеризуются высоким быстродействием, что достигается за счет использования

ими тактовых частот со значениями порядка сотен мегагерц. Так, их использование

в качестве опорных частот ![]() преобразования

позволяет существенно уменьшить длительность

преобразования

позволяет существенно уменьшить длительность ![]() цикла

преобразования для ПФИ последовательного принципа действия. В табл. 3.3

приведены максимально допустимые значения частот преобразования

цикла

преобразования для ПФИ последовательного принципа действия. В табл. 3.3

приведены максимально допустимые значения частот преобразования ![]() для различных серий ПЛИС фирмы Xilinx и значения длительности

для различных серий ПЛИС фирмы Xilinx и значения длительности ![]() циклов линейного преобразования

циклов линейного преобразования ![]() для предложенных нейроструктур

ПФИ

для предложенных нейроструктур

ПФИ ![]() .

.

Из табл. 3.3 следует, что применение ПЛИС фирмы Xilinx,

особенно серий Virtex2, Virtex4 и Spartan2, позволяет существенно (почти на порядок) уменьшить

время цикла ![]() импульсно-цифровых

преобразователей, строившихся ранее на схемах со средним уровнем интеграции, за

счет увеличения внутрикристальных частот.

импульсно-цифровых

преобразователей, строившихся ранее на схемах со средним уровнем интеграции, за

счет увеличения внутрикристальных частот.

Максимально допустимые значения частот преобразования для ПЛИС Xilinx *

|

Серия ПЛИС |

Максимальная внутренняя частота |

Длительность цикла преобразования с погрешностью δ= 0,025 % (n = 12) |

Длительность цикла преобразования с погрешностью δ= 0,0015 % (n = 16) |

|

Virtex |

200 |

20.48 мкс |

327.68 мкс |

|

Virtex E |

320 |

12.80 мкс |

204.80 мкс |

|

Virtex2 |

420 |

9.75 мкс |

156.00 мкс |

|

Virtex4 |

500 |

8.19 мкс |

131.07 мкс |

|

Spartan |

80 |

51.2 мкс |

819.2 мкс |

|

Spartan2 |

200 |

20.48 мкс |

327.68 мкс |

|

XC9500XL |

200 |

20.48 мкс |

327.68 мкс |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.