4 ТЕСТИРОВАНИЕ РАЗРАБАТЫВАЕМОГО УСТРОЙСТВА

FPGA не имеет какого-либо компонента программного обеспечения, лишь сигналы и схемы. Они обычно имеют внешний вид такой, как порты подсоединённые к шинам для получения и отправки информации. Шины в другом направлении подсоединены к другим деталям компьютера или к другим компьютерам. Для данного проекта, чтобы проверить получается ли правильный сигнал на выходе компонента ключа деталей компьютера, было решено использовать программное обеспечение для генерации ключей и сообщений, посылая их по граничным компонентам деталей и сопоставляя результаты.

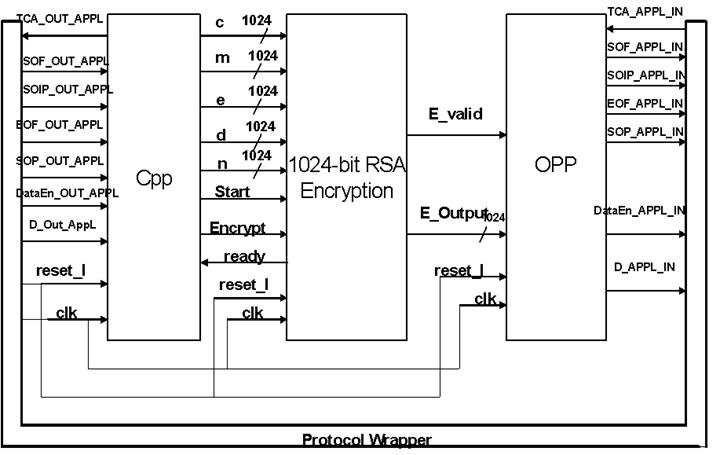

Подробнее, используется исполнение RSA алгоритма на JAVA языке для генерации общего ключа d, малого ключа е, исходного сообщения m и закодированного сообщения с. Ниже показана краткая схема:

Во время вычисления конструкции компонентов также были использованы функции компонентов GMP C Library, чтобы сгенерировать и выполнить шестизначные вычисления. Таким образом, необходимо было сопоставить результаты сгенерированные деталями компьютера. Так как в деталях все данные бинарны, то легко сгенерировать и просмотреть шестизначные числа. Также, с помощью сравнения видно, что GMP имеет более большую целочисленную библиотеку шины, чем класс Java BigInteger.

Часть тестирования этого проекта включает в себя программы и периферийные схемы деталей компьютера. Программное обеспечение RSA, которое использовалось - MyRSA java программа, написанная Бобби Кенни(borrisoleigh@hotmail.com). В соответствии с длиной ключей приходится резервировать данные на входе и выходе. Однако, методы резервирования различны. 1024-битное значение может занять 32 часовых цикла для проведения захвата в то время, как каждая строка пакета сообщений обрабатывается за один часовой цикл. Выходные данные с OPP модуля могут принять не больше 256 бит входных данных, поэтому также имеется модуль( не показанный графически), который резервирует выходное значение и посылает 4 последовательных пакета сообщений OPP модулю.

Protocol Wrapper управляет заголовком пакетов, сокращает объём работы внутри модулей. Он требует некоторой задержки для окончания обработки данных входящих пакетов сообщений и имеет ограниченную полосу пропускания для отсылки пакетов сообщений.

В дальнейших деталях структура машины выполнена в CPP модуле. Слово читается в 32-битном буфере каждый часовой цикл. После всего значения для кодирования и/или декодирования получены и после проверки, что сигнал “ready” от RSA модуля кодирования в порядке, он потом высылает сигнал “start” RSA модулю кодирования, а также сигналы нескольких 1024-битных значений. OPP модуль будет генерировать пакеты сообщений всякий раз, когда он обнаружит ‘e_valid” сигнал. Между внутренними модулями и внешними пакетами сообщений имеется около семи входных и выходных сигналов. В схеме триггеры не были нарисованы на границах для основного пространства. Триггеры гарантируют синхронизацию посылки и отправки сигналов на внутренние компоненты. После того, как OPP модуль создаёт пакеты сообщений, можно сопоставить значение с программно вычисленным результатом.

В этом проекте была выполнена схема 1024-битной SRA в VHDL. Это полнофункциональная схема RSA, включающая ключ генерации и данные кодирования. Компонент ключа генерации RSA и компонент данных кодирования слишком велики, чтобы подойти к единственной Xilinx Virtex 2000E FPGA на FPX платформе, поэтому невозможно протестировать их на реальных деталях. Для этого каждый подкомпонент был эмитирован на ModelSim и показал функциональную корректность. Также ни ключ генерации RSA, ни компонент данных кодирования не могут быть протестированы на FPX, однако были выполнены все тестирования связанных деталей, включая CPP и OPP.

Компонент кодирования забирает 79% от всех ресурсов FPGA, пока тестер на простоту сам забирает 84% от всех ресурсов FPGA. Поэтому ни ключ генерации, ни компонент кодирования не могут подходить FPX платформе.

В соответствии с синтезом статистики самой высокой частотой компонента кодирования RSA является 64.3 МГц. Таким образом, предполагаемая производительность для 1024-битного d - 0.45 кб/с, а для 3-битного е – 137 кб/с.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.