Оглавление

1. Общие сведения 3

1.1. Постановка задачи 3

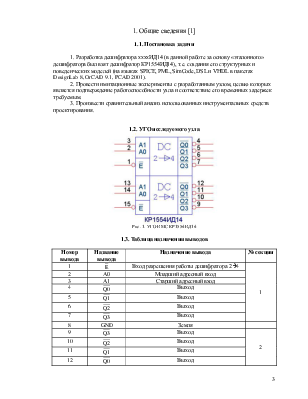

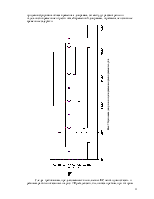

1.2. УГО исследуемого узла 3

1.3. Таблица назначения выводов 3

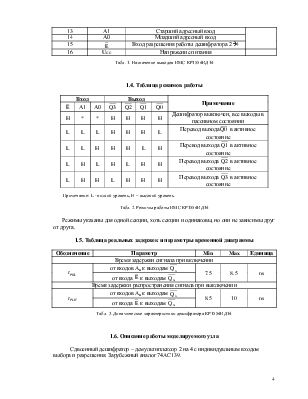

1.4. Таблица режимов работы 4

1.5. Таблица реальных задержек и параметры временной диаграммы 4

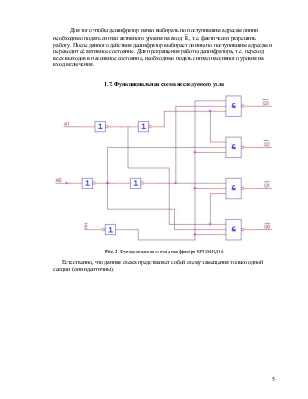

1.6. Описание работы моделируемого узла 4

1.7. Функциональная схема исследуемого узла 5

2. Проектирование элемента в Design Lab 8.0 6

2.1. Условное графическое изображение проектируемого узла

в виде иерархического символа 6

2.2. Схема замещения проектируемого узла 6

2.3. Текстовое SPICE-описание моделируемого узла 8

2.3.1. Содержимое файла Test_ShemZamesh.cir 8

2.3.2. Содержимое файла Test_ShemZamesh.net 8

2.4. Содержимое файла описания внешних воздействий 9

2.5. Схема верификации иерархического символа 10

2.6. Результаты моделирования узла 11

2.7. Оценка предельных скоростных (частотных) возможностей

исследуемого узла 13

2.8. Функциональное описание проектируемого узла с помощью

примитивов LOGICEXP, PINDLY и CONSTRAINT 16

2.9. Схема верификации символа с подключенной к нему макромоделью 17

3. Проектирование элемента в OrCad 9.1 20

3.1. Иерархический символ (УГО, схема замещения) 20

3.2. Схема верификации иерархического символа 23

3.3. Результаты моделирования узла 23

3.4. Поведенческая VHDL-модель проектируемого узла 25

3.5. УГО проектируемого узла, подключение к нему

VHDL-модели и верификация её 27

4. Проектирование элемента в PCAD 2001 29

4.1. Макромодель, представленная иерархическим символом 29

4.2. Условное графическое обозначение узла для PML модели

4.3. Поведенческая модель на языке PML 31

4.4. Схема верификации иерархического символа и узла, поддерживаемого

PML-моделью 33

4.5. Результаты логического моделирования узла в пакете PCAD 34

4.6. Результаты логико-временного моделирования элемента с учетом

реальных задержек 35

5. Заключение 37

6. Литература 41

7. Приложение (дерево файлов) 42

1. Общие сведения [1]

1.1. Постановка задачи

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.