Результаты моделирования будут показаны следующим образом, сначала будет

|

Следуя требованиям,

предъявляемым к выполнению КР, необходимо сказать о режимах работы показанных

на рис. 7. Прежде всего, был показан режим, при котором выключен дешифратор,

т.е. при ![]() = H все выходы

дешифратора находятся в пассивном состоянии (

= H все выходы

дешифратора находятся в пассивном состоянии (![]() ).

Участок от 0-50ns. Далее дешифратор включается и идет

режим переключения адресов и соответствующих им выходов (см. табл. 2). Участок

50-200ns. После прохода по всем адресам (их всего

четыре), дешифратор переводится в состояние «выключен», т.е. в исходное

состояние. Участок 200-250ns.

).

Участок от 0-50ns. Далее дешифратор включается и идет

режим переключения адресов и соответствующих им выходов (см. табл. 2). Участок

50-200ns. После прохода по всем адресам (их всего

четыре), дешифратор переводится в состояние «выключен», т.е. в исходное

состояние. Участок 200-250ns.

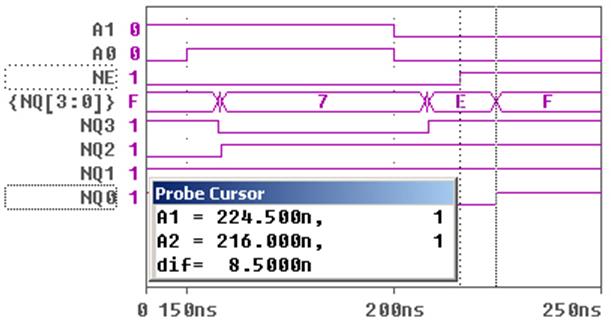

Так же на временной диаграмме можно заметить быстрое переключение шинного сигнала при переключении с одного адреса на другой, данные переключения вызваны разными временными задержками при включении и выключении от адресных входов до информационных и в результате получается, что-то типа «иголки» только наоборот, т.е. дешифратор около 1ns работает не совсем стабильно.

В принципе, по данной временной диаграмме можно судить о правильности функционального описания проектируемого элемента. Далее будет показаны участки временной диаграммы (рис. ХХХ), на которых явно указаны временные задержки в различных ситуациях работы дешифратора.

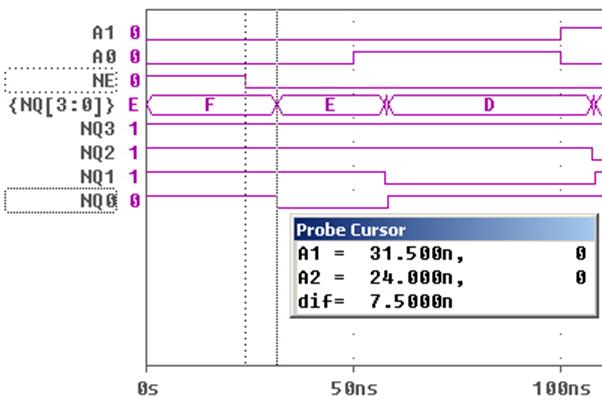

Рис. 8. Участок № 1.

Участок временной диаграммы, на

котором явно показано время задержки между включением дешифратора и выводом

данных, т.е. время ![]() и оно соответствует минимальному

значению задержки реального дешифратора.

и оно соответствует минимальному

значению задержки реального дешифратора.

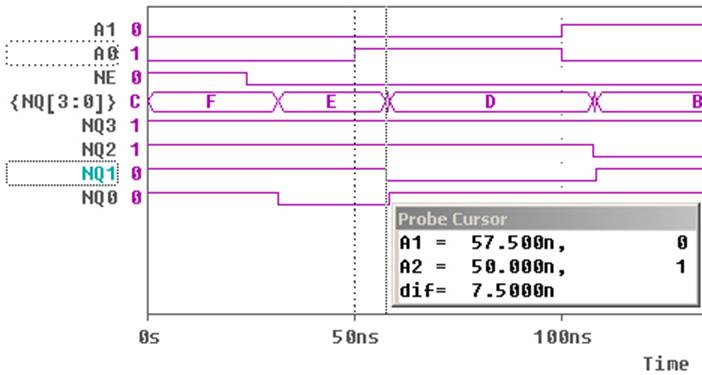

Рис. 9. Участок № 2.

Участок временной диаграммы, на

котором показано время задержки распространения сигнала между переключением

адреса и включением данных, т.е. время ![]() .

.

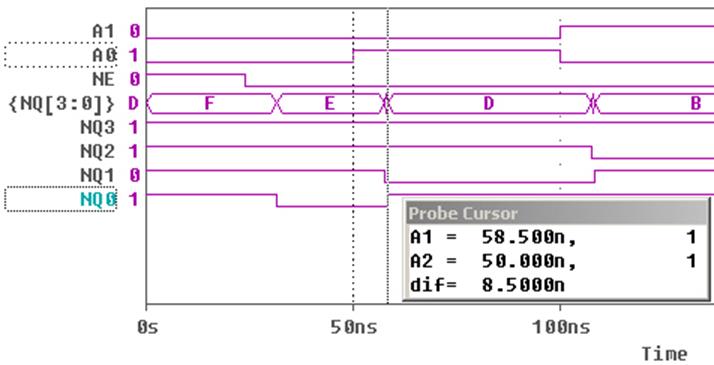

Рис. 10. Участок № 2.

Как раз на

данном рисунке показана ситуация противоположная ситуации показанной на рис. 9,

т.е. показано время выключения сигнала по адресному входу ![]() .

.

Рис. 11. Участок № 2.

На данном

рисунке показана ситуация противоположная ситуации показанной на рис.8, т.е.

показано время задержки распространения сигнала от входа включения дешифратора

до выводов данных при выключении дешифратора ![]() .

.

Собственно, все задержки, показанные на временных диаграммах, идентичны табличным (см. табл. 3), что соответственно, говорит о правильности имитирования временных задержек.

Вообщем, данный пункт подтвердил, что разработанная схема замещения полностью удовлетворяет как требованиям функционального устройства элемента, так и требованиям по динамическим характеристикам разрабатываемого элемента.

2.7. Оценка предельных скоростных (частотных) возможностей исследуемого узла

Собственно, необходимо немного сказать о методике исследования предельных

скоростных возможностей. Заранее ясно, что частота не может быть выше заложенной в модель задержек, так что интересно конечно смотреть на сообщения, которые выдает MicroSimProbe, но можно заранее сказать, какие предельные частотные возможности. В данном случае MicroSimProbe при нарушении каких-либо временных нарушений почему-то сообщения об ошибках не выдает, что очень странно. Сначала было предположение о каких либо ошибках при проектировании элемента, но при установки эталонного, т.е. имеющегося в библиотеке 74AC элемента 74AC139, также сообщений о каких-либо ошибках выведено не было.

Исходя из выше сказанного, приводятся примеры на временной диаграмме, при которых из-за не соблюдения временных соотношений нарушается логика работы моделируемого узла.

Первые

два примера относятся к случаям работы с сигналом ![]() .

.

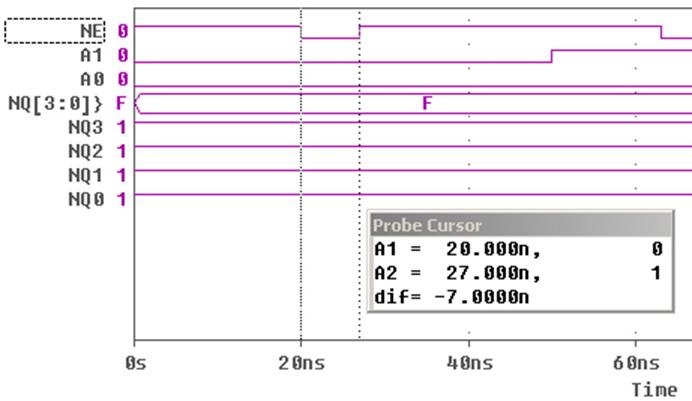

Рис. 12. Пример №1 нарушения временных соотношений.

На рис. 12

приведен пример, того как время удержания сигнала ![]() мало

для того, чтобы схема успела среагировать и дешифратор «включился» на работу.

Данное время не должно быть менее чем время

мало

для того, чтобы схема успела среагировать и дешифратор «включился» на работу.

Данное время не должно быть менее чем время ![]() = 7.5ns, в примере данное время равно 7ns

(в дальнейшем, при рассмотрении других примеров, преподаватель должен понимать,

что контрольное время удержания сигнал при котором происходит временное

нарушение показано на соответствующем примеру рисунке). Следовательно, частота

работы по данному входу на включение дешифратора не должна быть более чем

= 7.5ns, в примере данное время равно 7ns

(в дальнейшем, при рассмотрении других примеров, преподаватель должен понимать,

что контрольное время удержания сигнал при котором происходит временное

нарушение показано на соответствующем примеру рисунке). Следовательно, частота

работы по данному входу на включение дешифратора не должна быть более чем  Гц = 133 MГц.

Гц = 133 MГц.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.