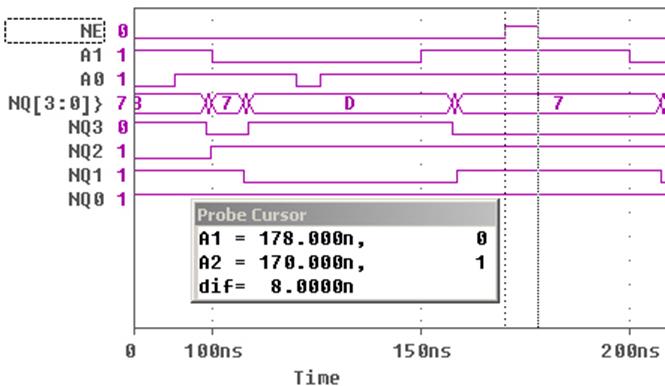

Рис. 13. Пример № 2 нарушения временных соотношений

На рис. 13

показан случай, при котором за то время удержания сигнала выключения

дешифратора он не выключается, что собственно и является нарушением логики

работы схемы. Следовательно, время удержания сигнала ![]() не

должно быть менее чем данное время

не

должно быть менее чем данное время ![]() = 8.5 ns.

Следовательно, частота повторения сигнала выключения дешифратора должна быть:

= 8.5 ns.

Следовательно, частота повторения сигнала выключения дешифратора должна быть:  Гц = 117 МГц.

Гц = 117 МГц.

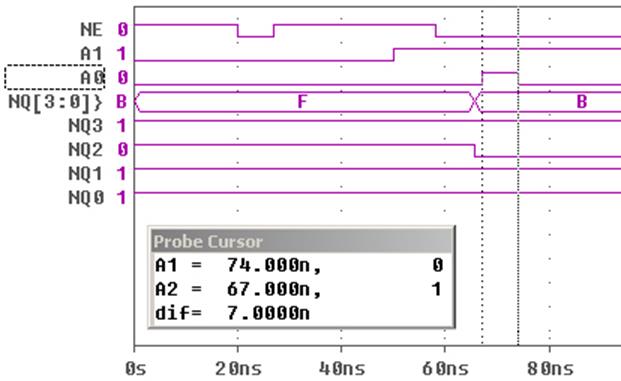

Следующие два примера относятся к случаям работы с входами Ax

Рис. 14. Пример № 3 нарушения временных соотношений

Время удержание сигнала

адреса настолько мало, что схема не успевает отреагировать должным образом, время

удержания сигнала адреса, при переходе из LàH,

должно быть не менее ![]() = 7.5 ns.

Таким образом, частота переключения сигнала должна быть не более

= 7.5 ns.

Таким образом, частота переключения сигнала должна быть не более  Гц = 133 MГц.

Гц = 133 MГц.

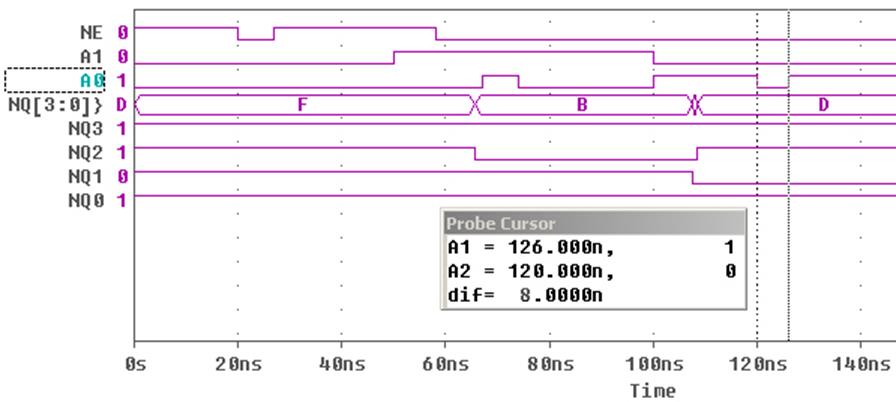

Рис. 15. Пример №4, нарушения временных соотношений

Время удержание

сигнала адреса настолько мало, что схема не успевает отреагировать должным

образом, время удержания сигнала, при переходе с HàL,

адреса должно быть не менее ![]() = 8.5 ns.

Таким образом, частота переключения сигнала должна быть не более

= 8.5 ns.

Таким образом, частота переключения сигнала должна быть не более  Гц = 117 МГц.

Гц = 117 МГц.

2.8. Функциональное описание проектируемого узла с помощью примитивов LOGICEXP, PINDLY и CONSTRAINT и оформление его в виде макромодели

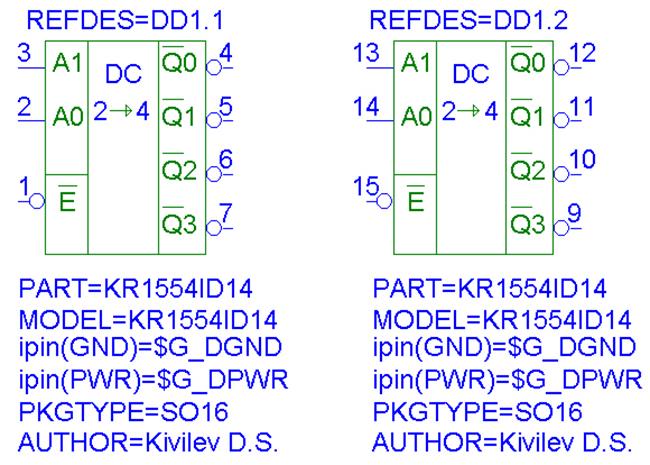

Рис. 16. УГО символа использующего для функционального описания макромодель

*************КР1554ИД14 Сдвоенный дешифратор 2->4*******************

**Директива начала макромодели

.SUBCKT KR1554ID14 EBAR_I A0_I A1_I Q0BAR_O Q1BAR_O Q2BAR_O Q3BAR_O

+ OPTIONAL: DPWR=$G_DPWR DGND=$G_DGND

+ PARAMS: MNTYMXDLY=0 IO_LEVEL=0

**Логический блок. Здесь зашита функциональность элемента

U1554ID14LOG LOGICEXP (3,7) DPWR DGND

+ EBAR_I A0_I A1_I

+ EBAR A0 A1 *входы в логический блок

+ Q0BAR Q1BAR Q2BAR Q3BAR *выходы из лог. блока

+ D0_GATE IO_STD

+ IO_LEVEL={IO_LEVEL}

+

+ LOGIC: *логическая секция

+ EBAR = { EBAR_I }

+ A0 = { A0_I }

+ A1 = { A1_I }

+ A0BAR = { ~A0 }

+ A1BAR = { ~A1 }

+ ENABLE = { ~EBAR }

+ Q0BAR = { ~(ENABLE & A1BAR & A0BAR ) }

+ Q1BAR = { ~(ENABLE & A1BAR & A0 ) }

+ Q2BAR = { ~(ENABLE & A1 & A0BAR ) }

+ Q3BAR = { ~(ENABLE & A1 & A0 ) }

** Блок задержек. Он отвечает за моделируемые временные задержки

U1554ID14DLY PINDLY (4,0,3) DPWR DGND

+ Q0BAR Q1BAR Q2BAR Q3BAR * для четырех линий вычисляется задержка

+ EBAR A0 A1 *а это те самые сигналы от которых зависят те самые задержки

+ Q0BAR_O Q1BAR_O Q2BAR_O Q3BAR_O * а вот это выходные линии из данного блока

+ IO_STD

+ MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL}

+

+ BOOLEAN: *переменные переключения сигнала

+ ABLE = { CHANGED(EBAR,0) }

+ ADDR = { CHANGED(A0,0) | CHANGED(A1,0) }

+

+ PINDLY: *ну вот и самое главное, где «генерируются» задержки

+ Q0BAR_O Q1BAR_O Q2BAR_O Q3BAR_O = {

+ CASE (

+ ADDR & TRN_LH, DELAY(-1NS,8.5NS, 10NS),

+ ADDR & TRN_HL, DELAY(-1NS,7.5NS, 8.5NS),

+ ABLE & TRN_LH, DELAY(-1NS,8.5NS,10NS),

+ ABLE & TRN_HL, DELAY(-1NS,7.5NS, 8.5NS),

+ DELAY(7.0NS,7.0NS,10.0NS)

+ )

+ }

.ENDS

Небольшая оговорка, при задании временных задержек в функции DELAY первый параметр = -1, т.е. на место средней задержки поставлена минимальная.

А вообще, по сравнению с VHDL такое описание очень гибко задает время распространения сигналов, т.е. можно задать максимальный путь и минимальный, тогда как в VHDL пришлось бы изворачиваться (см. гл. 3).

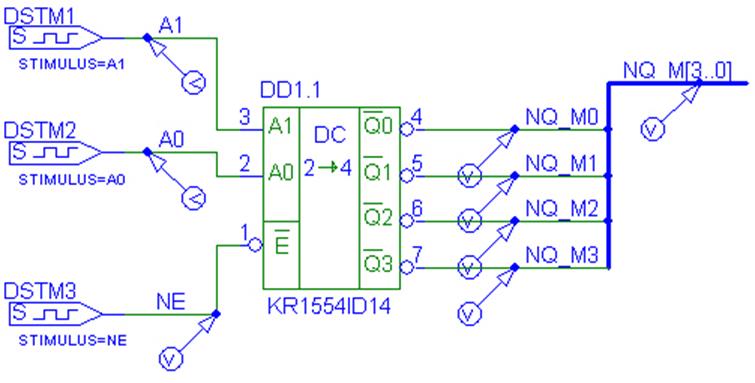

Рис. 17. Схема верификации элемента с подключенной макромоделью

В данной схеме (рис. 17) выходные сигналы помечены как NQ_Mx, т.е. обозначение отражает, то свойство схемы, что производится верификация элемента с макромоделью.

Далее приводится временная диаграмма работы данного элемента. Естественно, что тестовые сигналы идентичны сигналам тестирования элемента в п.2.6. Фактически приведенная диаграмма идентична временной диаграмме приведенной на рис.7. Исходя из выше сказанного, приводится один пример задержек.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.