\\\\\Q1\\\\_-2\ : OUT std_logic;

\\\\\Q2\\\\_-2\ : OUT std_logic;

\\\\\Q3\\\\_-2\ : OUT std_logic

);

end;

ARCHITECTURE model OF \КР1554ИД14\ IS

SIGNAL N1 : std_logic;

SIGNAL N2 : std_logic;

SIGNAL N3 : std_logic;

SIGNAL N4 : std_logic;

SIGNAL N5 : std_logic;

SIGNAL N6 : std_logic;

SIGNAL N7 : std_logic;

SIGNAL N8 : std_logic;

SIGNAL N9 : std_logic;

SIGNAL N10 : std_logic;

BEGIN

process(\\\\\E\\\\_-1\,\\\\\E\\\\_-2\) begin

if (\\\\\E\\\\_-1\'EVENT) then--проверка на переключение сигнала \\E\-1\

case (\\\\\E\\\\_-1\)is

when '1' => N1 <= not(\\\\\E\\\\_-1\)after 5 ns;--Tplh

when '0' => N1 <= not (\\\\\E\\\\_-1\)after 3.5 ns;--Tphl

end case;

end if;

if (\\\\\E\\\\_-2\'EVENT) then--проверка на переключение сигнала \\E\-2\

case (\\\\\E\\\\_-2\)is

when '1' => N6 <= not(\\\\\E\\\\_-2\)after 5 ns;--Tplh

when '0' => N6 <= not (\\\\\E\\\\_-2\)after 3.5 ns;--Tphl

end case;

end if;

end process;

---------------Для первой секции------------------------

N2 <= (\A0_-1\) after 3.5 ns; -- Задержки при адресных входах, при вкл

N3 <= (\A1_-1\) after 3.5 ns;

N4 <= not ( \A0_-1\) after 4.5 ns; -- и выкл.

N5 <= not (\A1_-1\) after 4.5 ns;

---------------Для второй секции------------------------

N7 <= (\A0_-2\) after 4.5 ns;

N8 <= (\A1_-2\) after 4.5 ns;

N9 <= not ( \A0_-2\) after 5.5 ns;

N10 <= not (\A1_-2\) after 5.5 ns;

\\\\\Q0\\\\_-1\ <= not ( N4 and N5 and N1 ) after 4 ns;

\\\\\Q1\\\\_-1\ <= not ( N2 AND N5 and N1 ) after 4 ns;

\\\\\Q2\\\\_-1\ <= not ( N4 AND N3 and N1 ) after 4 ns;

\\\\\Q3\\\\_-1\ <= not ( N2 AND N3 and N1 ) after 4 ns;

\\\\\Q0\\\\_-2\ <= not ( N9 AND N10 and N6 ) after 4 ns;

\\\\\Q1\\\\_-2\ <= not ( N10 AND N7 and N6 ) after 4 ns;

\\\\\Q2\\\\_-2\ <= not ( N9 AND N8 and N6 ) after 4 ns;

\\\\\Q3\\\\_-2\ <= not ( N7 AND N8 and N6 ) after 4 ns;

END model;

Модель на VHDL проста и логична, но с моделированием временных задержек пришлось помучиться. В задании сказано, что надо предусмотреть контроль временных соотношений, но реализация данного требования не имеет места быть, по причине отсутствия знаний разработчика в данной области (к сожалению).

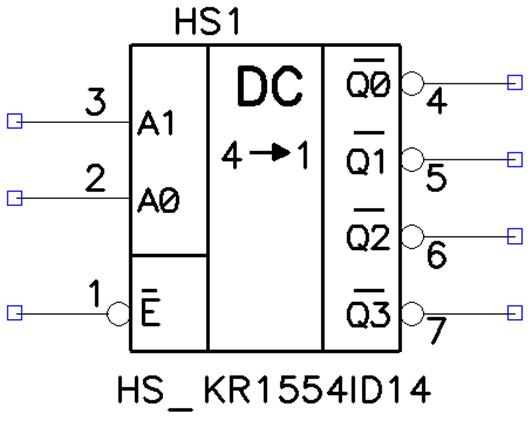

3.5. УГО проектируемого узла, подключение к нему VHDL-модели и верификация её.

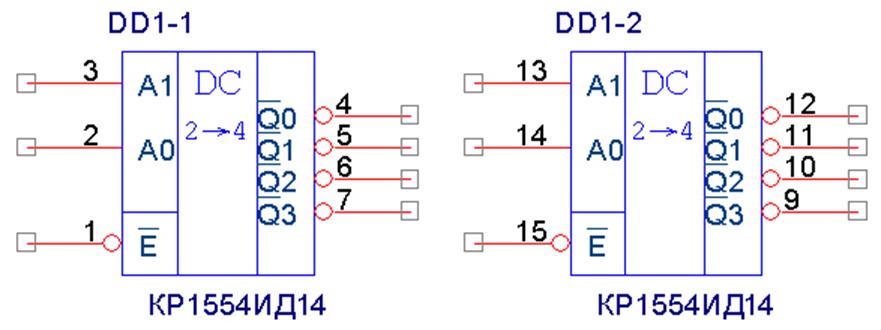

Рис. 28. УГО символа с подключенной VHDL-моделью

На рис. 28 специально показаны две секции ИМС для проверки преподавателем правильности задания упаковочной информации.

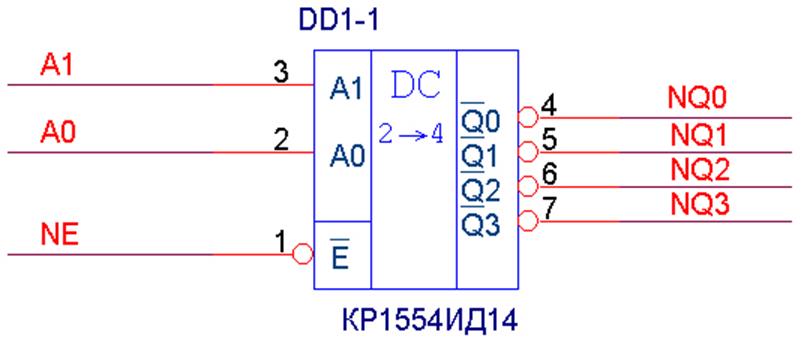

Рис. 29. Схема верификации созданного элемента

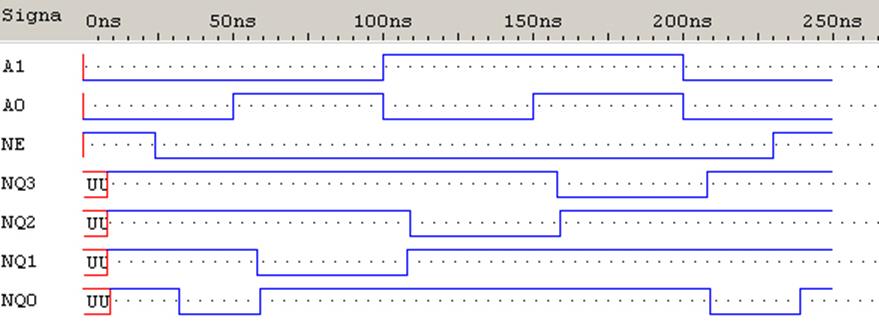

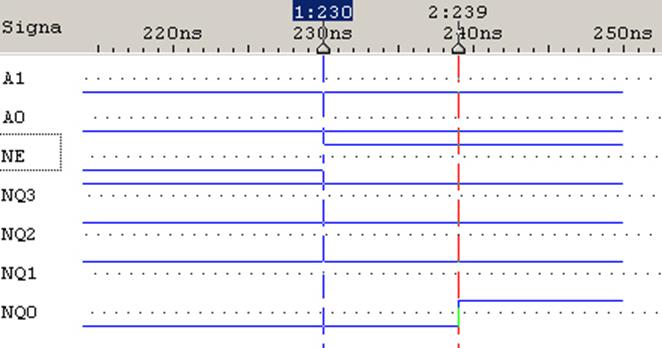

Рис. 30. Временная диаграмма моделируемого узла

Собственно, рассматривая ВД

представленную на рис. 30, можно отметить правильность логического

функционирования элемента, а также идентичность временных задержек задержкам

представленным в табл.3 и на ВД рис. 23. Обычное, в данной работе, по

ситуационное рассмотрение задержек ограничится представлением времени вкл/выкл

дешифратора, т.е. время ![]() и

и ![]() соответственно.

соответственно.

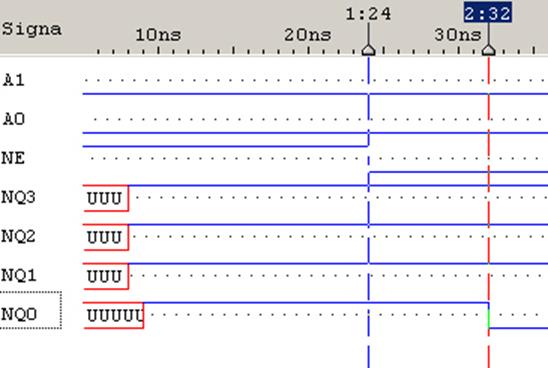

Рис. 31.

Участок временной диаграммы, временной задержки ![]()

Разница меток на рис.31

равна разнице меток на рис.24, что соответственно, говорит об идентичности

задержек ![]() для двух реализаций элемента.

для двух реализаций элемента.

Рис. 32.

Участок временной диаграммы, временной задержки ![]()

Такие же выводы можно сделать относительно рис.32. Разница меток на рис.32 соответствует разницы меток на рис. 27.

Вообщем, все задачи, поставленные перед разработчиком элемента в пакете OrCad успешно выполнены, данное обстоятельство подтверждается правильностью функционирования разработанного узла.

4. Проектирование элемента в PCAD 2001 [5]

4.1. Макромодель, представленная иерархическим символом

Рис. 33. УГО проектируемого символа представленного схемой замещения

Надо сказать, что в данном описании также как и в описании символа в OrCad (см. п.3.1.), применена маленькая хитрость, а именно отображаемое имя и фактическое имя вывода не совпадают, разница заключается в знаке инверсии.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.