end;

--=============== Инвертор =======================---------------

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

entity \К155ЛН1\ is

port (

\IN_-1\ : IN std_logic;

\OUT_-1\ : OUT std_logic;

VCC : IN std_logic;

GND : IN std_logic;

\IN_-2\ : IN std_logic;

\OUT_-2\ : OUT std_logic;

\IN_-3\ : IN std_logic;

\OUT_-3\ : OUT std_logic;

\IN_-4\ : IN std_logic;

\OUT_-4\ : OUT std_logic;

\IN_-5\ : IN std_logic;

\OUT_-5\ : OUT std_logic;

\IN_-6\ : IN std_logic;

\OUT_-6\ : OUT std_logic

);

END ;

architecture model of \К155ЛН1\ is

begin

\OUT_-1\ <= not \IN_-1\;

\OUT_-2\ <= not \IN_-2\;

\OUT_-3\ <= not \IN_-3\;

\OUT_-4\ <= not \IN_-4\;

\OUT_-5\ <= not \IN_-5\;

\OUT_-6\ <= not \IN_-6\;

end;

Схема замещения на рис. 21 ничем принципиальным от схемы на рис. 4 не отличается (разве, что графикой). Но есть одна особенность, в принципе такая же как и на рис. 4. Она заключается в обозначении портов, точнее отображения знака инверсии. Поиск каких-нибудь ухищрений в обозначении входов на элементе или портах не проводился. Поэтому пришлось немного «схитрить». В УГО символа указывались названия выводов без инверсии, соответственно нет знака инверсии, а раз его нет, то его можно нарисовать.

Пользователю библиотеки без разницы, каким способом поставлен знак инверсии, и поэтому данный способ жизнеспособен.

Стоит оговорить заранее, что данный способ не применялся при проектировании символа с VHDL-моделью.

3.2. Схема верификации иерархического символа

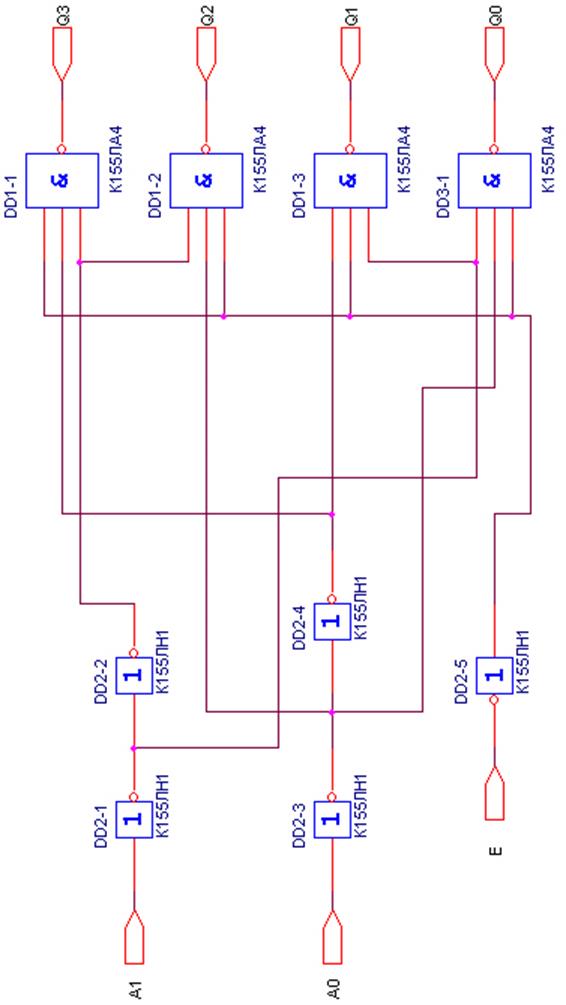

Рис. 22. Схема верификации проектируемого символа

3.3. Результаты моделирования узла

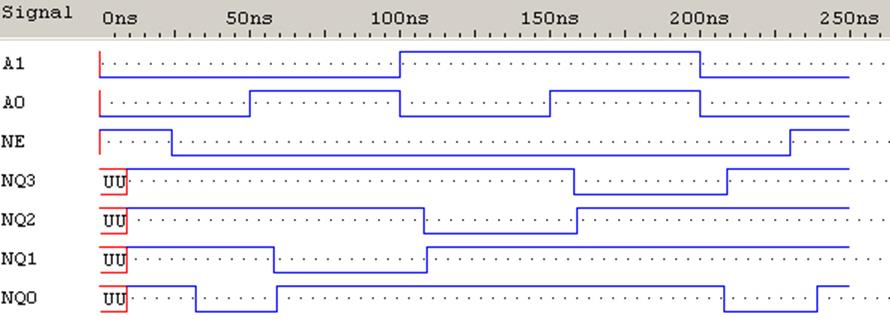

Рис. 23. Временная диаграмма работы дешифратора (в общем виде).

Данная временная диаграмма аналогична временной диаграмме на рис. 7. В принципе,

логика функционирования узла очевидна. Далее приводятся временные задержки в различных ситуациях. Ситуации, аналогичны ситуациям, рассматриваемым в п. 2.6.

В выводе результатов есть некоторая неточность, т.е. время округляется до ns, поэтому значение 7.5ns отображается как 8ns и т.п.

К сожалению, данный пакет не выводит окошко с разницей времени между 2-я маркерами, поэтому разница во времени считается как время установки 1-го маркера минус время установки 2-го маркера.

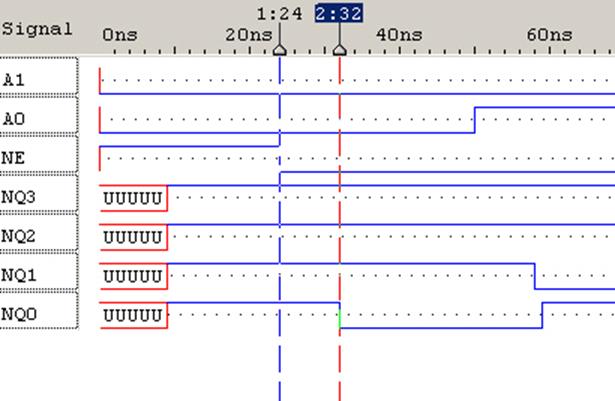

Рис. 24. Ситуация № 1.

Участок временной

диаграммы, на котором явно показано время задержки между включением дешифратора

и выводом данных, т.е. время ![]() .

.

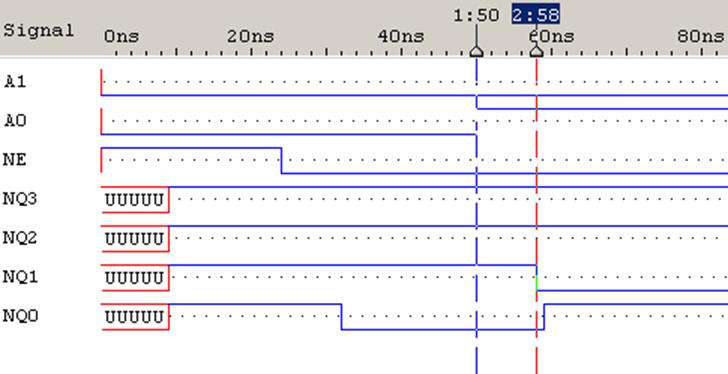

Рис. 25. Ситуация № 2.

Участок временной диаграммы, на котором показано время

задержки распространения сигнала между переключением адреса и включением

данных, т.е. время ![]() .

.

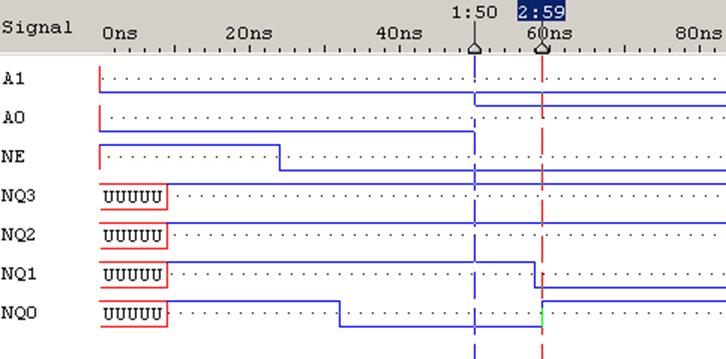

Рис. 26. Ситуация № 3.

На данном рисунке показана ситуация противоположная

ситуации показанной на рис. 25, т.е. показано время выключения сигнала по

адресному входу ![]() .

.

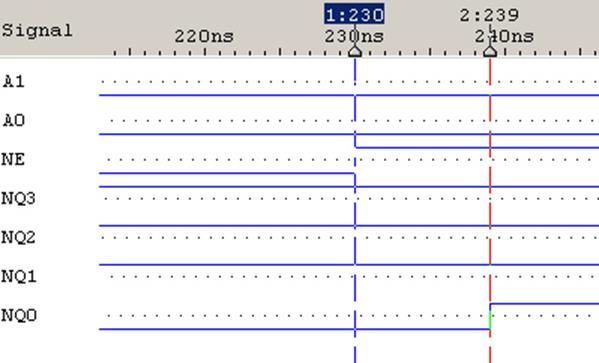

Рис. 27. Ситуация № 4.

На данном рисунке показана ситуация противоположная ситуации показанной на

рис. 24, т.е. показано время задержки распространения

сигнала от входа включения дешифратора до выводов данных при выключении

дешифратора ![]() .

.

Исходя из полученных временных диаграмм, можно считать, что по функциональным и динамическим параметрам разработанный элемент соответствует своему физическому аналогу.

3.4. Поведенческая VHDL-модель проектируемого узла

--=========== Проектируемый дешифратор КР1554ИД14 ====================

entity \КР1554ИД14\is

port (

\A1_-1\ : IN std_logic;

\A0_-1\ : IN std_logic;

\\\\\E\\\\_-1\ : IN std_logic;

\\\\\Q0\\\\_-1\ : OUT std_logic;

\\\\\Q1\\\\_-1\ : OUT std_logic;

\\\\\Q2\\\\_-1\ : OUT std_logic;

\\\\\Q3\\\\_-1\ : OUT std_logic;

VCC : IN std_logic;

GND : IN std_logic;

\A1_-2\ : IN std_logic;

\A0_-2\ : IN std_logic;

\\\\\E\\\\_-2\ : IN std_logic;

\\\\\Q0\\\\_-2\ : OUT std_logic;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.