ricc_val= (MIN_TYP_MAX(i_param: NULL, 2500, 1250));

STATE Q0 Q1 Q2 Q3=ZERO;

EXIT;

END;

//установка параметров выхода

DRIVE Q0 Q1 Q2 Q3=(v0=vol_param,v1=voh_param,ttlh=tt_val,tthl=tt_val);

//установка параметров входов

LOAD E_LD,A0_LD,A1_LD=(v0=vol_param,r0=ril_val,v1=voh_param,

r1=rih_val,io=1e9,t=1p);

//логика работы проектируемого элемента

EXT_TABLE tblIndex

E A1 A0 Q3 Q2 Q1 Q0

1 0 0 H H H H

1 0 1 H H H H

1 1 0 H H H H

1 1 1 H H H H

0 0 0 H H H L

0 0 1 H H L H

0 1 0 H L H H

0 1 1 L H H H;

LOAD VCC_LD = (v0=gnd_param,r0=ricc_val,t=1p);

IF (warn_param) THEN

BEGIN

END;

//задержки на выход при 0->1 или 1->0.

DELAY Q0 Q1 Q2 Q3=

CASE (TRAN_LH) : tplh_val

CASE (TRAN_HL) : tphl_val

END;

EXIT;

4.4. Схема верификации иерархического символа и узла, поддерживаемого PML-моделью

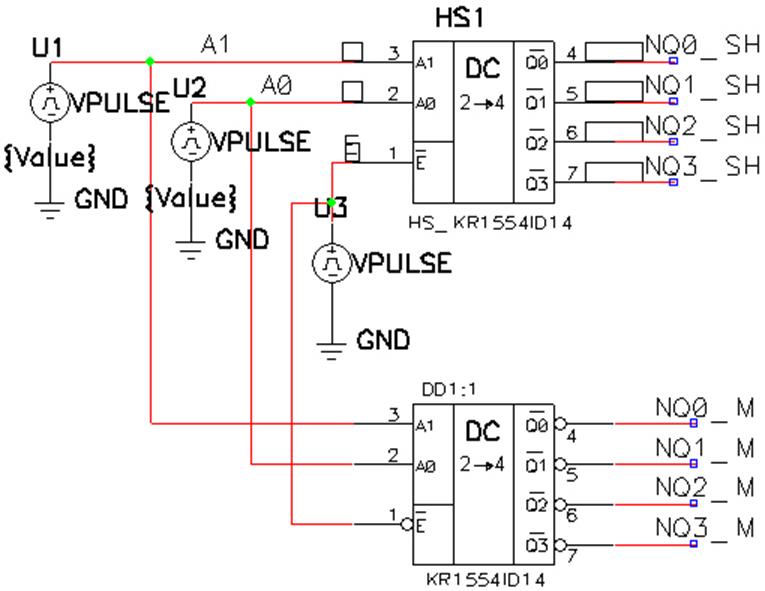

Рис. 36. Схема верификации 2-х реализаций проектируемого символа

В принципе, про данную схему можно сказать многое, но этому будет посвящен один из абзацев гл. 5.

4.5. Результаты логического моделирования узла в пакете PCAD

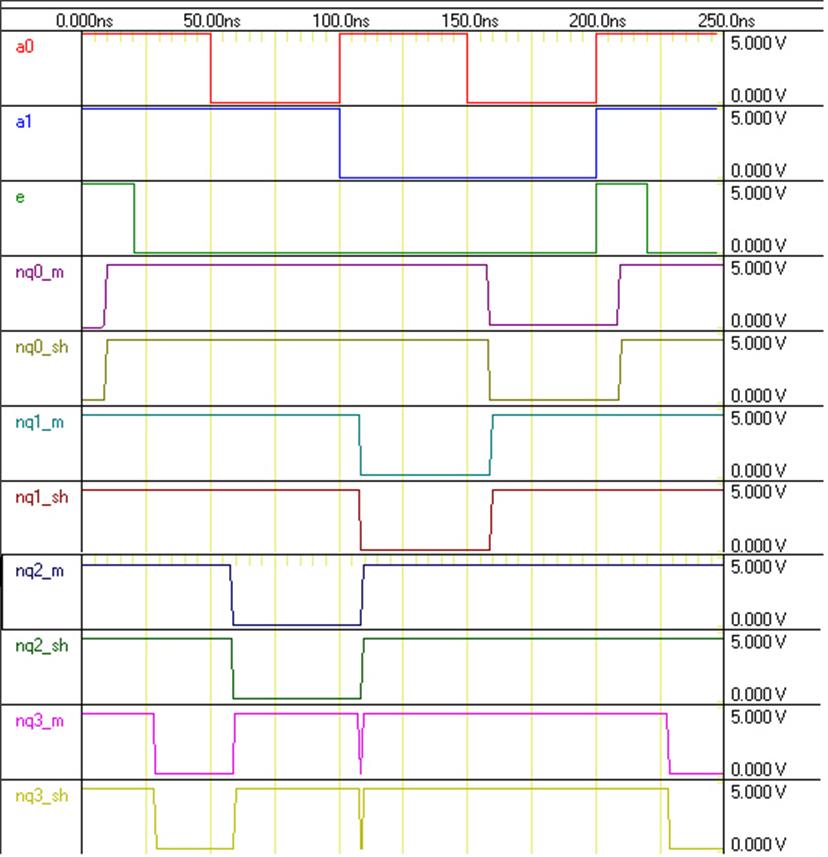

Временная диаграмма построена некоторым иным способом, чем результирующие временные диаграммы, построенные в других САПР, т.е. сначала идет «прогон» для старших адресов, затем для младших. Все временные соотношения соблюдены, логика работы узла также соответствует правильной работе реального элемента. Вообще же, данный пункт был разобран (дважды) в предыдущих главах, поэтому нецелесообразно повторяться.

К сожалению, те средства которые предоставляет PCAD по отображению сигналов, не совсем удобны, поэтому приходилось изворачиваться для предоставления данных результатов (рис. 37).

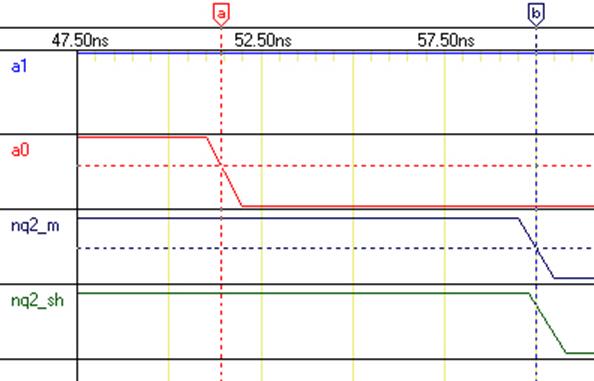

Рис. 37. Временная диаграмма работы моделируемого элемента в различных вариантах его реализации

4.6. Результаты логико-временного моделирования элемента с учетом реальных задержек

В данном пункте в качестве результатов логико-временной работы используется

рис. 37, т.к. при моделировании элемента учитывались временные задержки. Поэтому в данном пункте будут приведены некоторые фрагменты временной диаграммы (рис. 37), по аналогии с предыдущими главами.

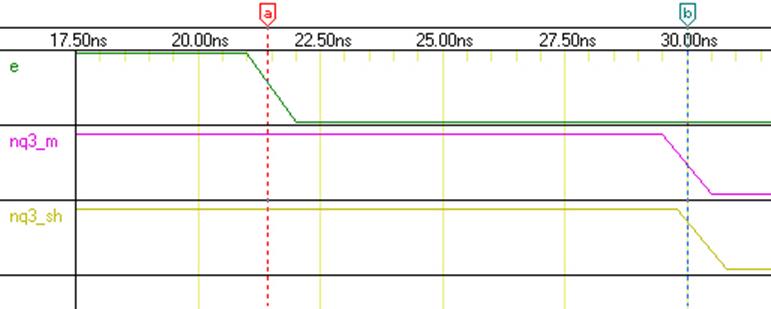

Рис. 38.

Участок временной диграммы, на котором показано ![]() .

.

Участок временной диаграммы, на котором показано время

задержки между включением дешифратора и выводом данных, т.е. время ![]() . Разница между маркерами равна »8.5 ns, что на 1ns больше чем положено по табл.3.

. Разница между маркерами равна »8.5 ns, что на 1ns больше чем положено по табл.3.

Данный факт объясняется тем, что продолжительность фронта и спада = 1ns, т.к. измерения проводятся от половины фронта/спада, то соответственно прибавляется по 0.5 секунд за переходной процесс.

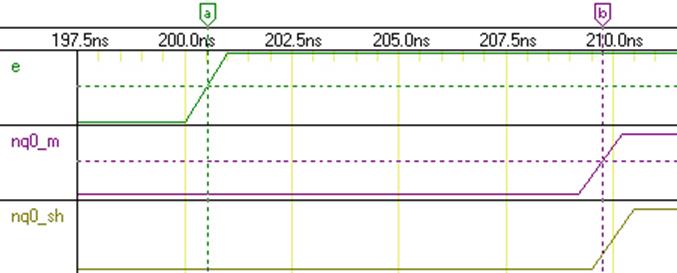

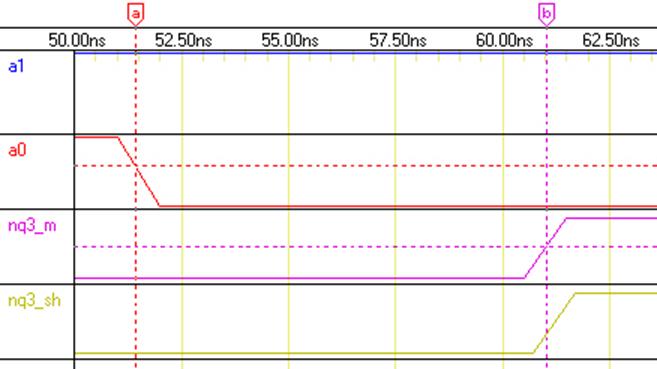

Рис. 39.

Участок временной диаграммы, на котором показано ![]() .

.

Участок временной диаграммы, на котором показано время

задержки между включением дешифратора и выводом данных, т.е. время ![]() . Разница между

маркерами равна »9.5 ns,

т.е. реально 8.5 ns, что соответствует значению

приведенному в табл. 3.

. Разница между

маркерами равна »9.5 ns,

т.е. реально 8.5 ns, что соответствует значению

приведенному в табл. 3.

Рис. 40.

Участок временной диаграммы, на котором показано ![]() .

.

Участок временной диаграммы,

на котором показано время задержки распространения сигнала между переключением

адреса и включением данных, т.е. время ![]() равное

7.5ns.

равное

7.5ns.

Рис. 41.

Участок временной диаграммы, на котором показано ![]()

Участок временной диаграммы, на котором показано время

задержки распространения сигнала между переключением адреса и включением

данных, т.е. время ![]() равное 8.5ns.

равное 8.5ns.

Вообщем судя по полученным временным диаграммам, динамические характеристики проектируемого элемента идентичны эталонным (см. табл. 3).

В целом, результаты моделирования в данном САПР вполне удовлетворяют поставленным требованиям разработки цифрового узла.

К сожалению, не был приведен командный файл (должен был бы быть п.4.5.), т.к., по просту, отсутствуют знания как и где его искать, это конечно минус ( - 0.х баллов).

5. Заключение

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.