МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ ФЕДЕРАЦИИ

ФЕДЕРАЛЬНОЕ АГЕНТСТВО ПО ОБРАЗОВАНИЮ

НОВОСИБИРСКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

Кафедра Вычислительной техники

Расчетно-графическая работа

по дисциплине

«Моделирование»

Часть 2

Факультет: АВТ Преподаватель:

Группа: АМ-609 к.т.н., доцент

Студент: Минина К. Шалагинов А. В.

Вариант 57

|

Содержание

1. Разработка потоковой VHDL- модели автомата без учета задержек. 3

2. Выводы.. 6

Список литературы.. 7

Приложение 1. 8

|

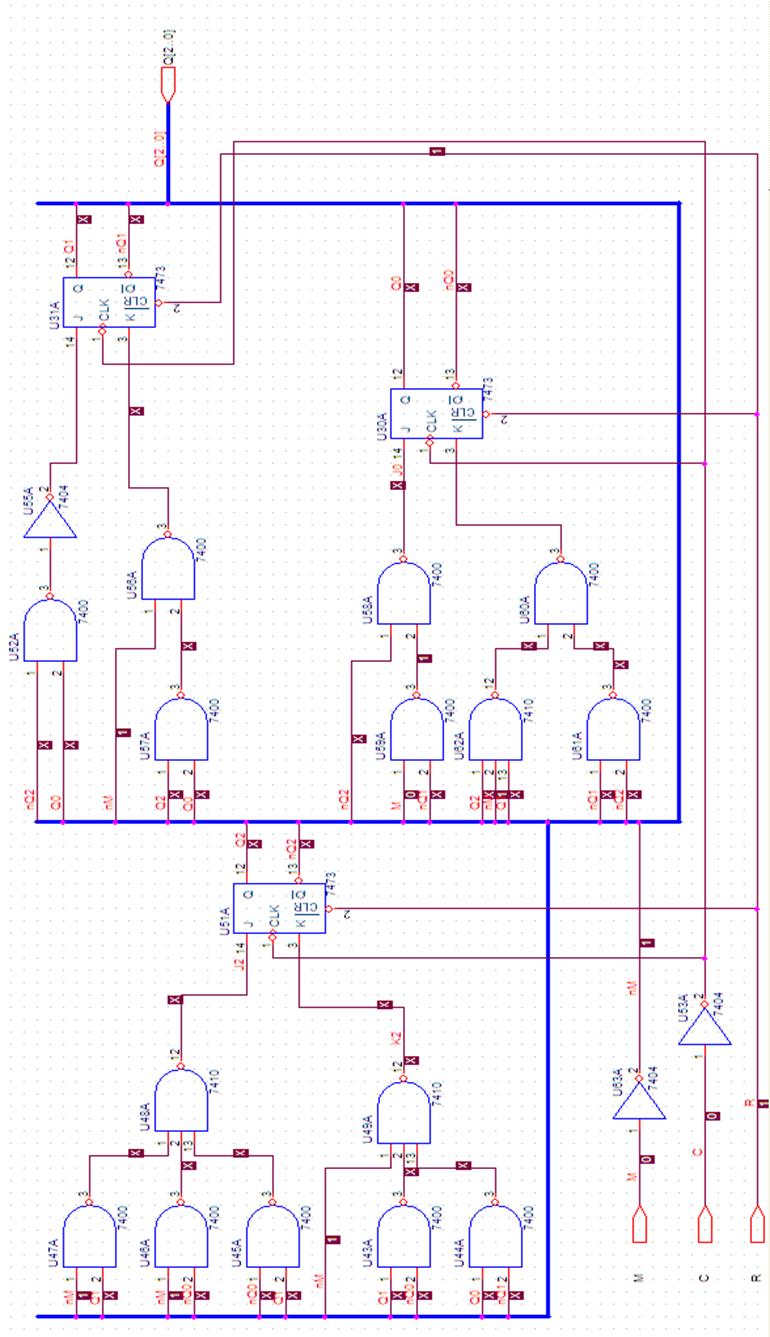

Листинг 1. Потоковая VHDL-модель цифрового автомата (Схема находится в приложении 1) |

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.std_logic_unsigned.all;

entity \Potoch_mod\ is

port(

M : in STD_LOGIC;

R : in STD_LOGIC;

C : in STD_LOGIC;

Q: out STD_LOGIC_VECTOR(2 downto 0)

);

end \Potoch_mod\;

architecture \Potoch_mod\ of \Potoch_mod\ is

signal NM,F1,F2,F3,F4,F5,F6,F7,F8,F9,F10,J0,

J1,J2,K0,K1,K2,NQ0,NQ1,NQ2: std_logic;

signal QP:std_logic_vector(2 downto 0);

begin

NM<= not M;

NQ0<=not QP(0);

NQ1<=not QP(1);

NQ2<=not QP(2);

F1<=not (NM and QP(1)) ;

F2<=not (NM and NQ0);

F3<=not (NQ0 and QP(1));

F4<=not (QP(1) and NQ0);

F5<=not (QP(0) and NQ1);

F6<=not (NQ2 and QP(0));

F7<=not (QP(0) and QP(2));

F8<=not (M and NQ1);

F9<=not (QP(2) and NM and QP(1));

F10<=not (NQ2 and NQ1);

J0<=not (NQ2 and F8) ;

J1<=not (F6);

J2<=not (F1 and F2 and F3);

K0<=not (F9 and F10) ;

K1<=not (F7 and NM) ;

K2<=not (NM and F4 and F5);

process(C,R)

begin

if(R='0') then QP <= (others => '0');

elsif(C='1' and C'EVENT) then

QP(2)<=(not(K2) and QP(2))or (J2 and not(QP(2)));

QP(1)<=(not(K1) and QP(1))or (J1 and not(QP(1)));

QP(0)<=(not(K0) and QP(0))or (J0 and not(QP(0)));

end if;

end process;

Q<=QP;

end \Potoch_mod\;

|

|

|

Рис. 1 – Временная диаграмма результатов моделирования построенных VHDL-моделей цифрового автомата |

И все-таки пришлось познакомиться с построением поточных моделей автомата. Это оказалось совсем не сложно после подробного изучения подобной работы в качестве примера. Надеюсь, что в будущем мне пригодятся полученные знания и бесценный опыт!)

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.