Министерство образования и науки РФ

Федеральное агентство по образованию

Новосибирский государственный технический университет

|

Кафедра Вычислительной техники

Расчётно – графическая работа

по дисциплине «Моделирование»

«Проектирование цифрового автомата в САПР OrCAD 9.1 и Active-HDL 8.1»

Факультет: АВТ

Группа: АМ - 610

Студенты: Баласов Д. И.

Вариант: 5

Преподаватель: Шалагинов А. В.

Новосибирск,

2009

Оглавление

Постановка задачи. 3

Краткое описание объекта проектирования. 4

Условное графическое обозначение (УГО) проектируемого цифрового автомата. 4

Назначение выводов схемы: 4

Логическая таблица. 5

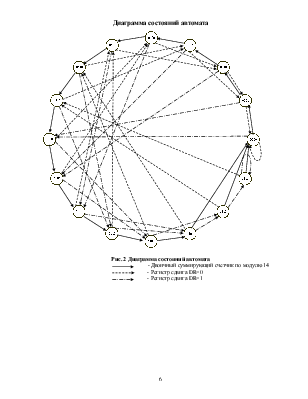

Диаграмма состояний автомата. 6

Синтез цифрового автомата с комбинационной частью на логических элементах. 7

Синтез двоичного суммирующего счётчика по модулю 14. 7

Синтез регистра сдвига в сторону младших разрядов. 8

Реализация спроектированного автомата в виде иерархического блока со схемой замещения на зарубежных библиотечных компонентах. 9

Разработка абстрактных символов, поддерживаемых VHDL-моделями. 12

Реализация спроектированного автомата в виде иерархического блока со схемой замещения на абстрактных символах. 15

Разработка функциональной VHDL-модели цифрового автомата. 19

Разработка потоковой VHDL-модели цифрового автомата. 20

Синтез комбинационной части автомата на мультиплексорах с использованием разложения Шеннона. 23

Синтез комбинационной части ЦА на дешифраторах. 28

Синтез комбинационной части ЦА на ПЗУ.. 35

Выводы.. 40

Личные впечатления. 41

Список использованной литературы.. 42

Синтезировать четырёхразрядный цифровой автомат на JK-триггерах с комбинационной частью на логических элементах с двумя режимами работы, управляемый входным сигналом M. При M = 0 цифровой автомат выполняет функцию двоичного суммирующего счетчика по модулю 13, при M = 1 – вычитающего счётчика 1 из N. Сброс осуществляется высоким уровнем (R=1), автомат тактируется по фронту сигнала С.

Разработать абстрактные символы, поддерживаемые VHDL-моделями, используемых в проекте элементов. Спроектировать иерархический блок со схемой замещения на зарубежных библиотечных компонентах и на ранее созданных абстрактных символах.

Разработать функциональную, потоковую VHDL-модель автомата.

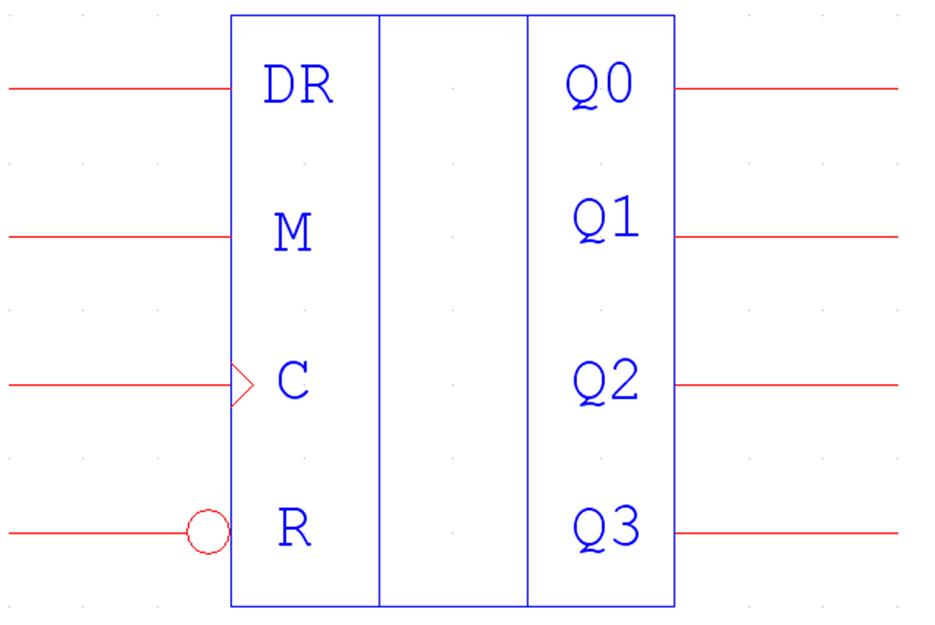

Рис. 1 УГО проектируемого автомата

Ø R – сброс счётчика;

Ø C – тактирующий сигнал (CLOCK);

Ø M – сигнал, задающий режим работы;

Ø [Q3, Q2,Q1,Q0]- выходные сигналы с JK-триггеров.

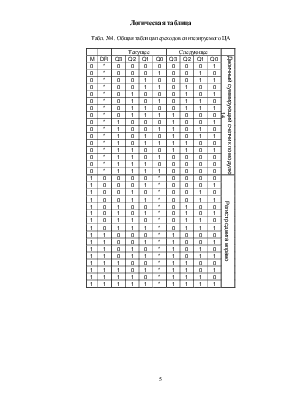

Табл. №1. Общая таблица переходов синтезируемого ЦА

|

Текущее |

Следующее |

|||||||||

|

M |

DR |

Q3 |

Q2 |

Q1 |

Q0 |

Q3 |

Q2 |

Q1 |

Q0 |

Двоичный суммирующий счетчик по модулю 14 |

|

0 |

* |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

|

0 |

* |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

|

|

0 |

* |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

|

|

0 |

* |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

|

|

0 |

* |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

|

|

0 |

* |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

|

|

0 |

* |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

|

|

0 |

* |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

|

|

0 |

* |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

|

0 |

* |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

|

|

0 |

* |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

|

|

0 |

* |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

|

|

0 |

* |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

|

|

0 |

* |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

|

|

0 |

* |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

|

|

0 |

* |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

|

|

1 |

0 |

0 |

0 |

0 |

* |

0 |

0 |

0 |

0 |

Регистр сдвига вправо |

|

1 |

0 |

0 |

0 |

1 |

* |

0 |

0 |

0 |

1 |

|

|

1 |

0 |

0 |

1 |

0 |

* |

0 |

0 |

1 |

0 |

|

|

1 |

0 |

0 |

1 |

1 |

* |

0 |

0 |

1 |

1 |

|

|

1 |

0 |

1 |

0 |

0 |

* |

0 |

1 |

0 |

0 |

|

|

1 |

0 |

1 |

0 |

1 |

* |

0 |

1 |

0 |

1 |

|

|

1 |

0 |

1 |

1 |

0 |

* |

0 |

1 |

1 |

0 |

|

|

1 |

0 |

1 |

1 |

1 |

* |

0 |

1 |

1 |

1 |

|

|

1 |

1 |

0 |

0 |

0 |

* |

1 |

0 |

0 |

0 |

|

|

1 |

1 |

0 |

0 |

1 |

* |

1 |

0 |

0 |

1 |

|

|

1 |

1 |

0 |

1 |

0 |

* |

1 |

0 |

1 |

0 |

|

|

1 |

1 |

0 |

1 |

1 |

* |

1 |

0 |

1 |

1 |

|

|

1 |

1 |

1 |

0 |

0 |

* |

1 |

1 |

0 |

0 |

|

|

1 |

1 |

1 |

0 |

1 |

* |

1 |

1 |

0 |

1 |

|

|

1 |

1 |

1 |

1 |

0 |

* |

1 |

1 |

1 |

0 |

|

|

1 |

1 |

1 |

1 |

1 |

* |

1 |

1 |

1 |

1 |

|

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.