else '0' after 14ns;

end OR2;

ü Логический элемент 16ИЛИ:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity OR16 is

port(

A15 : in STD_LOGIC;

A14 : in STD_LOGIC;

A13 : in STD_LOGIC;

A12 : in STD_LOGIC;

A11 : in STD_LOGIC;

A10 : in STD_LOGIC;

A9 : in STD_LOGIC;

A8 : in STD_LOGIC;

A7 : in STD_LOGIC;

A6 : in STD_LOGIC;

A5 : in STD_LOGIC;

A4 : in STD_LOGIC;

A3 : in STD_LOGIC;

A2 : in STD_LOGIC;

A1 : in STD_LOGIC;

A0 : in STD_LOGIC;

Q : out STD_LOGIC

);

end OR16;

--}} End of automatically maintained section

architecture OR16 of OR16 is

begin

-- enter your statements here --

Q<=A0 or A1 or A2 or A3 or A4 or A5 or A6 or A7 or A8 or A9 or A10 or A11 or A12 or A13 or A14 or A15;

end OR16;

ü Логический элемент 24ИЛИ:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity OR24 is

port(

A23 : in STD_LOGIC;

A22 : in STD_LOGIC;

A21 : in STD_LOGIC;

A20 : in STD_LOGIC;

A19 : in STD_LOGIC;

A18 : in STD_LOGIC;

A17 : in STD_LOGIC;

A16 : in STD_LOGIC;

A15 : in STD_LOGIC;

A14 : in STD_LOGIC;

A13 : in STD_LOGIC;

A12 : in STD_LOGIC;

A11 : in STD_LOGIC;

A10 : in STD_LOGIC;

A9 : in STD_LOGIC;

A8 : in STD_LOGIC;

A7 : in STD_LOGIC;

A6 : in STD_LOGIC;

A5 : in STD_LOGIC;

A4 : in STD_LOGIC;

A3 : in STD_LOGIC;

A2 : in STD_LOGIC;

A1 : in STD_LOGIC;

A0 : in STD_LOGIC;

Q : out STD_LOGIC

);

end OR24;

--}} End of automatically maintained section

architecture OR24 of OR24 is

begin

-- enter your statements here --

Q<=A0 or A1 or A2 or A3 or A4 or A5 or A6 or A7 or A8 or A9 or A10 or A11 or A12 or A13 or A14 or A15 or

A16 or A17 or A18 or A19 or A20 or A21 or A22 or A23;

end OR24;

Приведём схему замещения, построенную на спроектированных дешифраторах (рис. 19) и результаты верификации схемы с использованием дешифраторов (рис. 20).

Рис.19 Схема замещения с использованием дешифраторов

Рис. 20 Результаты верификации схемы на дешифраторах

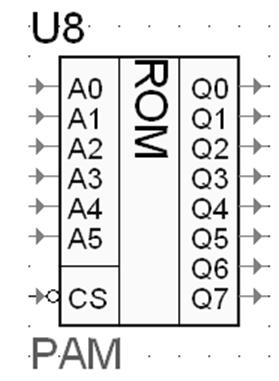

Синтез комбинационной части на ПЗУ сводится как бы к программированию памяти. Т.е. в памяти содержатся все возможные комбинации сигналов возбуждения.

В памяти хранится 64 слова по 8 бит каждое. На адресные входы памяти подаются аргументы функций возбуждения, и в зависимости от их значения выбирается одна единственная строчка, данные из памяти подаются на управляющие входы триггеров.

Рис. 21 УГО ПЗУ со входом разрешения CS (Chip Select)

Ниже приведен VHDL-код модуля памяти, реализованный с помощью оператора case, описаны все 64 возможные комбинации состояния аргументов функций:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity PAM is

port(

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.