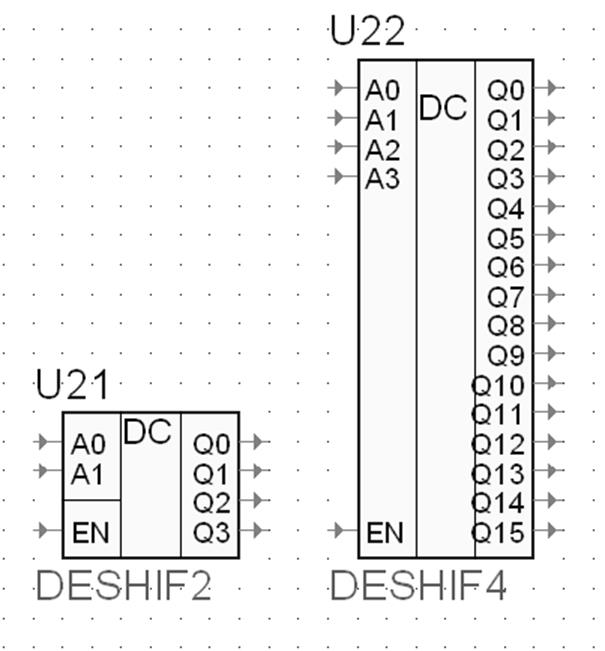

Рис.18 УГО дешифратора(2-4 слева, 4-16 справа)

ü VHDL-код дешифратора 2-4:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity DESHIF2 is

port(

A0 : in STD_LOGIC;

A1 : in STD_LOGIC;

EN : in STD_LOGIC;

Q0 : out STD_LOGIC;

Q1 : out STD_LOGIC;

Q2 : out STD_LOGIC;

Q3 : out STD_LOGIC

);

end DESHIF2;

architecture DESHIF2 of DESHIF2 is

begin

Q0<=not(A0) and not(A1) and EN;

Q1<=A0 and not(A1) and EN;

Q2<=not(A0) and A1 and EN;

Q3<=A0 and A1 and EN;

end DESHIF2;

ü VHDL-код дешифратора 4-16:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity DESHIF4 is

port(

EN : in STD_LOGIC;

A3 : in STD_LOGIC;

A2 : in STD_LOGIC;

A1 : in STD_LOGIC;

A0 : in STD_LOGIC;

Q15 : out STD_LOGIC;

Q14 : out STD_LOGIC;

Q13 : out STD_LOGIC;

Q12 : out STD_LOGIC;

Q11 : out STD_LOGIC;

Q10 : out STD_LOGIC;

Q9 : out STD_LOGIC;

Q8 : out STD_LOGIC;

Q7 : out STD_LOGIC;

Q6 : out STD_LOGIC;

Q5 : out STD_LOGIC;

Q4 : out STD_LOGIC;

Q3 : out STD_LOGIC;

Q2 : out STD_LOGIC;

Q1 : out STD_LOGIC;

Q0 : out STD_LOGIC

);

end DESHIF4;

architecture DESHIF4 of DESHIF4 is

begin

Q0<=not(A0) and not(A1)and not(A2)and not(A3)and EN;

Q1<=A0 and not(A1)and not(A2)and not(A3)and EN;

Q2<=not(A0) and A1 and not(A2)and not(A3)and EN;

Q3<=A0 and A1 and not(A2)and not(A3)and EN;

Q4<=not(A0) and not(A1)and A2 and not(A3)and EN;

Q5<=A0 and not(A1)and A2 and not(A3)and EN;

Q6<=not(A0) and A1 and A2 and not(A3)and EN;

Q7<=A0 and A1 and A2 and not(A3)and EN;

Q8<=not(A0) and not(A1)and not(A2)and A3 and EN;

Q9<=A0 and not(A1)and not(A2)and A3 and EN;

Q10<=not(A0) and A1 and not(A2)and A3 and EN;

Q11<=A0 and A1 and not(A2)and A3 and EN;

Q12<=not(A0) and not(A1)and A2 and A3 and EN;

Q13<=A0 and not(A1)and A2 and A3 and EN;

Q14<=not(A0) and A1 and A2 and A3 and EN;

Q15<=A0 and A1 and A2 and A3 and EN;

end DESHIF4;

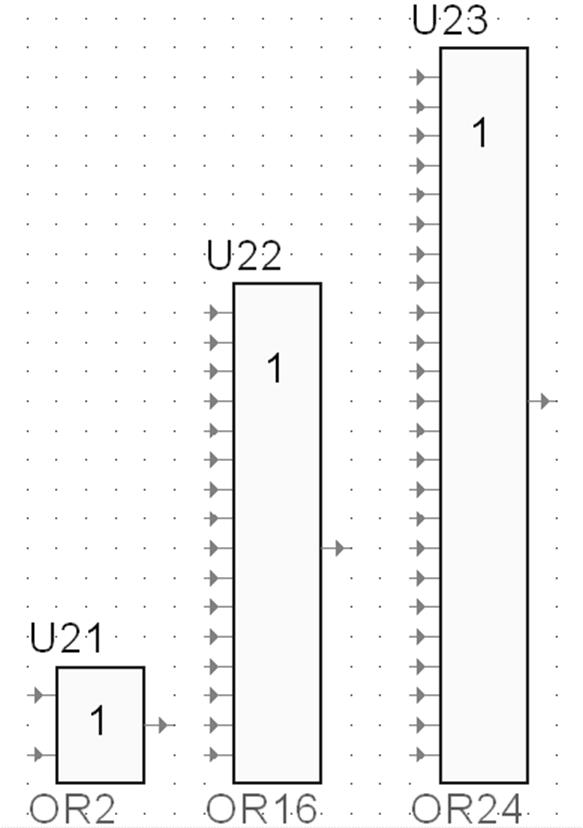

Рис.18 УГО элементов ИЛИ (на 2 входа, на 16 входов и на 24 входа)

Далее приведем VHDL-модели этих символов:

ü Логический элемент 2ИЛИ:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity OR2 is

port(

A : in STD_LOGIC;

B : in STD_LOGIC;

Q : out STD_LOGIC

);

end OR2;

--}} End of automatically maintained section

architecture OR2 of OR2 is

begin

-- enter your statements here --

Q<='1' after 10ns when (A or B)='1'

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.