Y : out STD_LOGIC

);

end NAND2;

--}} End of automatically maintained section

architecture NAND2 of NAND2 is

begin

Y<='1' after 11ns when (A and B)='0'

else '0' after 7ns;

end NAND2;

ü Инвертор:

ibrary IEEE;

use IEEE.STD_LOGIC_1164.all;

entity INV is

port(

A : in STD_LOGIC;

Q : out STD_LOGIC

);

end INV;

architecture INV of INV is

begin

-- enter your statements here --

Q<='1' after 12ns when A='0'

else '0' after 8ns;

end INV;

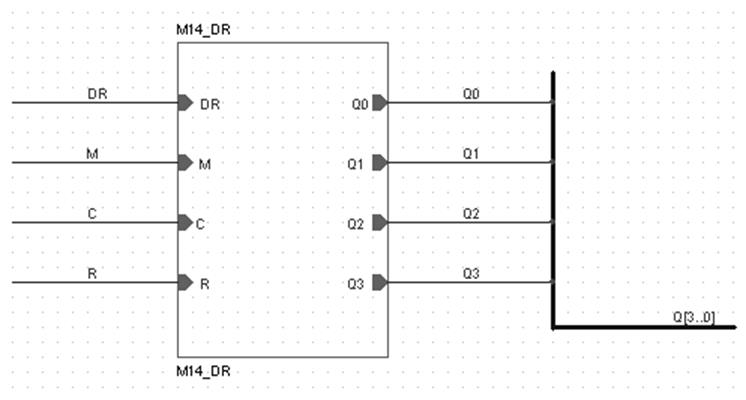

Рис. 7 Иерархический блок со схемой замещения на абстрактных элементах

На рисунке 7 показан иерархический блок со схемой замещения на спроектированных абстрактных символах, поддерживаемых VHDL – моделями. Понизив уровень иерархии на один уровень (раскрыв «черный ящик»), мы можем увидеть схему замещения (рис. 8).

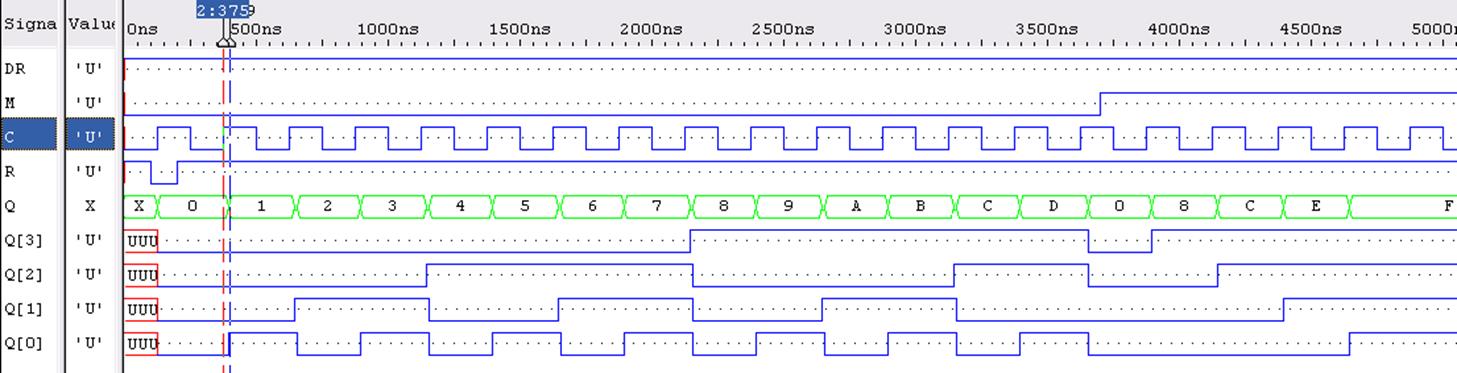

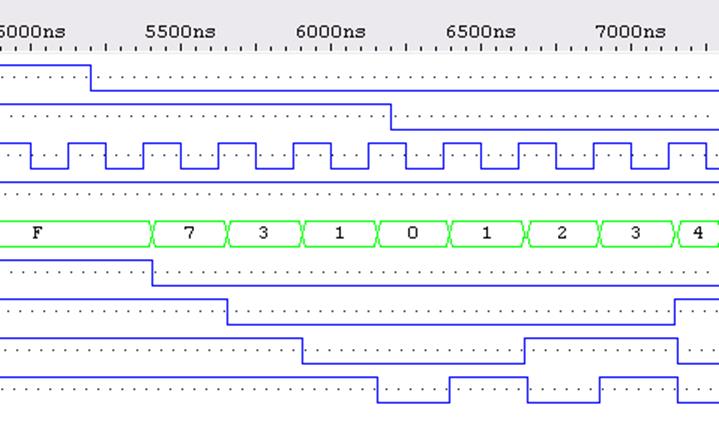

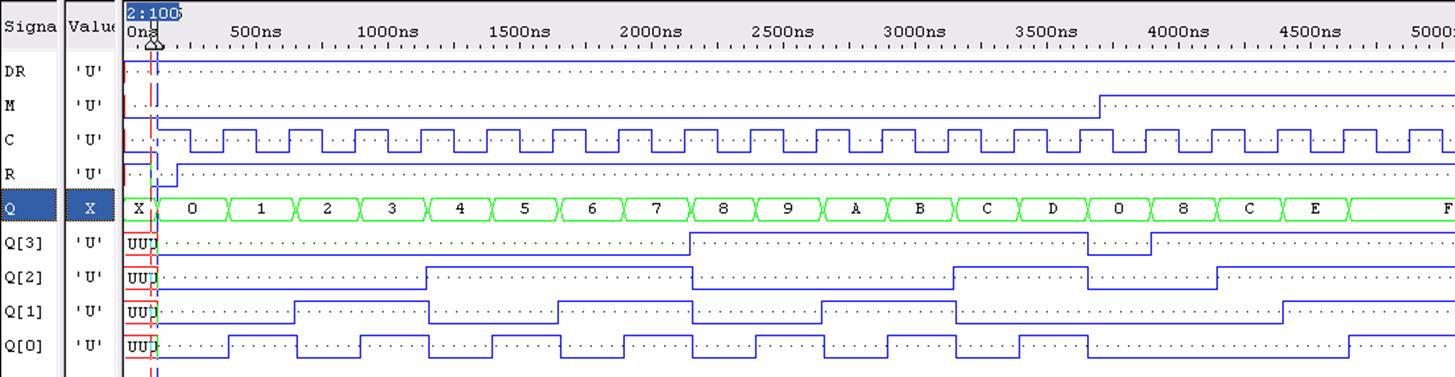

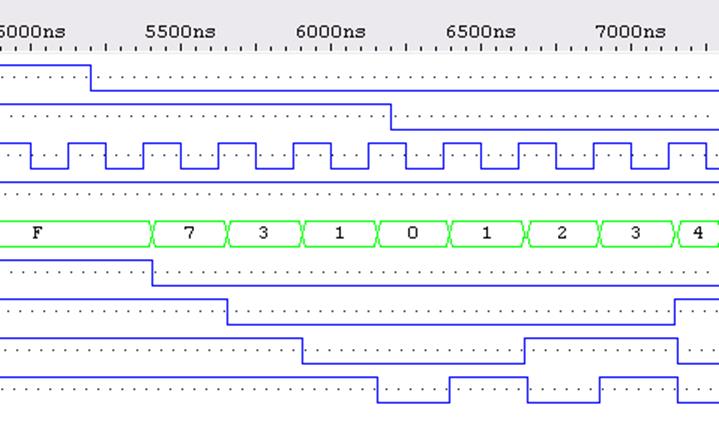

Как видно из временных диаграмм на рисунках 9, 9.1 задержки совпадают с задержками, полученными на зарубежных символах (рис. 5, рис 5.1).

Рис. 8 Схема замещения на абстрактных символах

Рис. 9 Результаты верификации схемы замещения на абстрактных символах (отображено время задержки по фронту С)

1 маркер стоит на точке 375ns, 2 маркер стоит на точке 399ns – задержка равна 24ns.

Рис. 9.1 Результаты верификации схемы замещения на абстрактных символах (отображено время задержки по сбросу R)

1 маркер стоит на точке 100ns, 2 маркер стоит на точке 125ns – задержка равна 25ns.

Определим некоторые закономерности двоичных счётчиков. Для прямого счета, можно отметить две закономерности:

1. Значение переменной Qi изменяется тогда, когда переменная в соседнем младшем разряде Qi-1 переходит из состояния «1» в состояние «0».

2. Значение выходной переменной Qi изменяется при поступлении очередного импульса счета в том случае, когда переменные во всех младших разрядах Qi-1, ..., Q1 находятся в состоянии «1». В нашем задании нужно разработать ЦА, который при значении сигнала М=0 будет выполнять функцию двоичного суммирующего счетчика по модулю 14, т.е. будет считать до D (1101) и сбрасываться в 0.

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.std_logic_unsigned.all;

entity \M14-DR_FUNC\ is

port(

M : in STD_LOGIC;

DR : in STD_LOGIC;

C : in STD_LOGIC;

R : in STD_LOGIC;

Q : out STD_LOGIC_VECTOR(3 downto 0)

);

end \M14-DR_FUNC\;

architecture \M14-DR_FUNC\ of \M14-DR_FUNC\ is

signal TEMP_QV : std_logic_vector(3 downto 0);

begin

process(M,C,DR,R)

begin

if (R='0') then TEMP_QV <= (others => '0');

elsif (C='1' and C'EVENT) then

if(M='0') then

if TEMP_QV>"1100" then TEMP_QV<="0000";

else TEMP_QV<=TEMP_QV+"0001";

end if;

else TEMP_QV <=DR & TEMP_QV(3 downto 1);

end if;

end if;

end process;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.