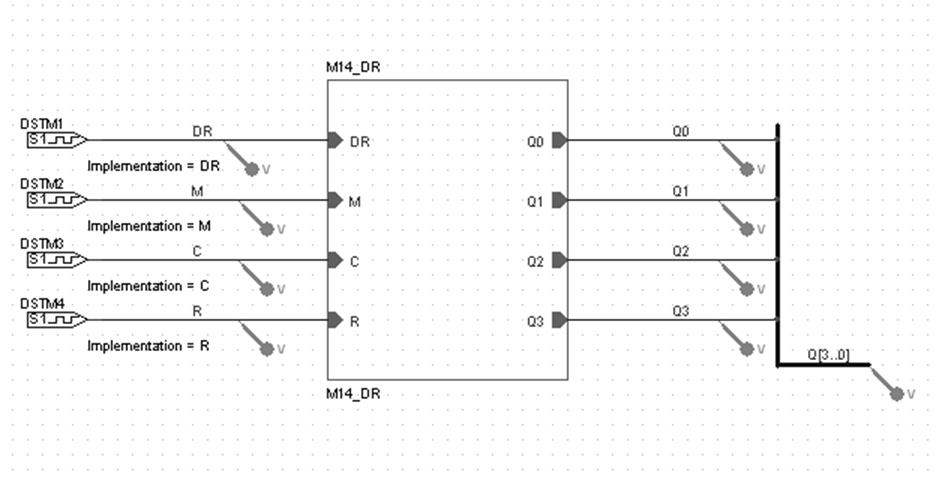

Рис. 3 Иерархический блок со схемой замещения на зарубежных логических элементах

На рисунке 3 показан иерархический блок со схемой замещения на зарубежных логических элементах. Понизив уровень иерархии на один уровень (раскрыв «черный ящик»), можно увидеть схему замещения (рис. 4). Её можно получить исходя из проведённого синтеза по построенным выражениям для функций возбуждения триггеров, предварительно переведенные в базис И-НЕ. Это сделано с целью увеличения быстродействия схемы, т.к. элементы И быстрее элементов ИЛИ; уменьшению разновидностей логических элементов, используемых в схеме, которые в последствии придется проектировать как VHDL-модели и не обнаружению элемента ИЛИ на четыре входа в стандартной библиотеке.

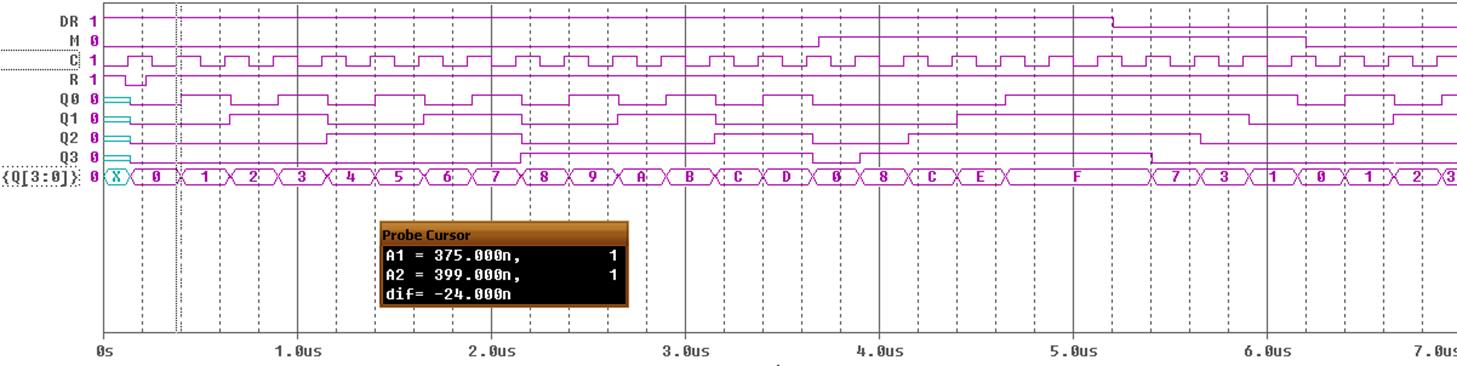

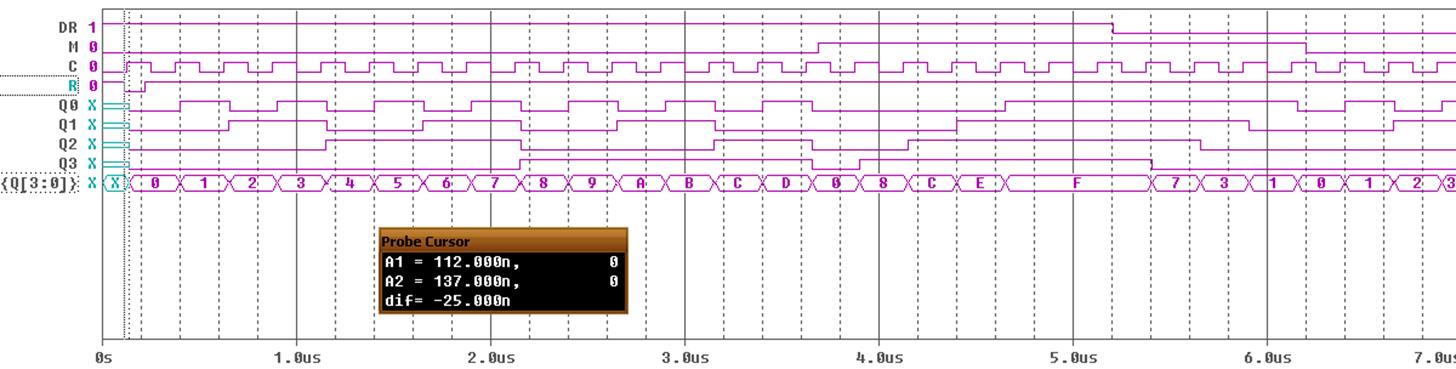

На рисунке 5 показаны результаты верификации схемы замещения на зарубежных символах, время задержки фронту С. На рисунке 5.1 показано время задержки по сбросу R.

Рис. 4 Схема замещения на зарубежных символах

Рис. 5 Результаты верификации схемы замещения на зарубежных символах (отображено время задержки по фронту С)

Рис. 5.1 Результаты верификации схемы замещения на зарубежных символах (отображено время задержки по сбросу R)

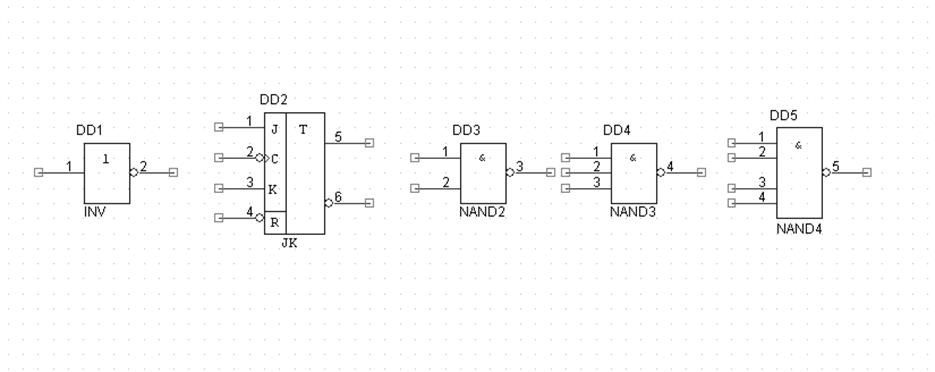

Ниже приведены УГО спроектированных абстрактных символов для реализации схемы замещения нашего ЦА:

Рис. 6 Спроектированные абстрактные символы

Далее приведем VHDL-модели всех символов:

ü JK – триггер, тактируемый фронтом и сбрасываемый низким уровнем сигнала R:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity JK is

port(

J : in STD_LOGIC;

K : in STD_LOGIC;

C : in STD_LOGIC;

R : in STD_LOGIC;

nQ : out STD_LOGIC;

Q : out STD_LOGIC

);

end JK;

architecture JK of JK is

signal Temp_Q: std_logic;

begin

process (J,C,K,R)

begin

if (R='0') then Temp_Q<='0' after 25ns;

elsif (C='0' and C'EVENT) then

if (J='1') then Temp_Q<='1'after 16ns;

elsif (J='0') then

if (K='0') then Temp_Q<=Temp_Q;

else Temp_Q<='0' after 25ns;end if;

else Temp_Q<='X';

end if;

end if;

end process;

Q<=Temp_Q;

nQ<=not Temp_Q;

end JK;

ü Логический элемент 4И-НЕ:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity NAND4 is

port(

A : in STD_LOGIC;

B : in STD_LOGIC;

C : in STD_LOGIC;

D : in STD_LOGIC;

Y : out STD_LOGIC

);

end NAND4;

--}} End of automatically maintained section

architecture NAND4 of NAND4 is

begin

Y<='1' after 12ns when (A and B and C and D)='0'

else '0' after 8ns;

end NAND4;

ü Логический элемент 3И-НЕ:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity NAND3 is

port(

A : in STD_LOGIC;

B : in STD_LOGIC;

C : in STD_LOGIC;

Y : out STD_LOGIC

);

end NAND3;

architecture NAND3 of NAND3 is

begin

Y<='1' after 11ns when (A and B and C)='0'

else '0' after 7ns;

end NAND3;

ü Логический элемент 2И-НЕ:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity NAND2 is

port(

A : in STD_LOGIC;

B : in STD_LOGIC;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.