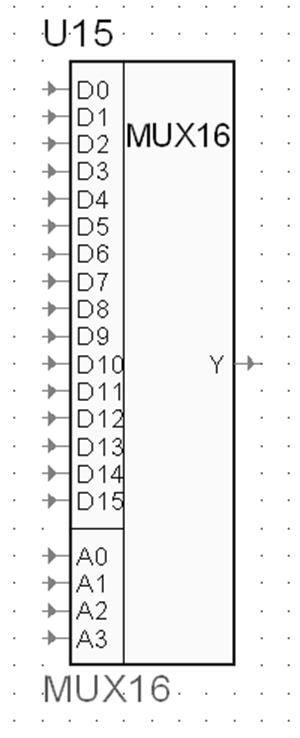

Рис. 15 УГО мультиплексора 16->1

ü VHDL-код мультиплексора 16 → 1:

ibrary IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.std_logic_unsigned.all;

entity MUX16 is

port(

A3 : in STD_LOGIC;

A2 : in STD_LOGIC;

A1 : in STD_LOGIC;

A0 : in STD_LOGIC;

D15 : in STD_LOGIC;

D14 : in STD_LOGIC;

D13 : in STD_LOGIC;

D12 : in STD_LOGIC;

D11 : in STD_LOGIC;

D10 : in STD_LOGIC;

D9 : in STD_LOGIC;

D8 : in STD_LOGIC;

D7 : in STD_LOGIC;

D6 : in STD_LOGIC;

D5 : in STD_LOGIC;

D4 : in STD_LOGIC;

D3 : in STD_LOGIC;

D2 : in STD_LOGIC;

D1 : in STD_LOGIC;

D0 : in STD_LOGIC;

Y : out STD_LOGIC

);

end MUX16;

--}} End of automatically maintained section

architecture MUX16 of MUX16 is

begin

-- enter your statements here --

Y<=(not(A0) and not(A1) and not(A2) and not(A3) and D0) or

(A0 and not(A1) and not(A2) and not(A3) and D1) or

(not(A0) and A1 and not(A2) and not(A3) and D2) or (A0 and A1 and not(A2) and not(A3) and D3) or

(not(A0) and not(A1) and A2 and not(A3) and D4) or (A0 and not(A1) and A2 and not(A3) and D5) or

(not(A0) and A1 and A2 and not(A3) and D6) or (A0 and A1 and A2 and not(A3) and D7) or

(not(A0) and not(A1) and not(A2) and A3 and D8) or (A0 and not(A1) and not(A2) and A3 and D9) or

(not(A0) and A1 and not(A2) and A3 and D10) or (A0 and A1 and not(A2) and A3 and D11) or

(not(A0) and not(A1) and A2 and A3 and D12) or (A0 and not(A1) and A2 and A3 and D13) or

(not(A0) and A1 and A2 and A3 and D14) or (A0 and A1 and A2 and A3 and D15);

end MUX16;

Далее приведём схему замещения, построенную на спроектированных мультиплексорах (рис. 16) и результаты верификации схемы с использованием мультиплексоров (рис. 17).

Рис.16 Схема замещения с использованием мультиплексоров

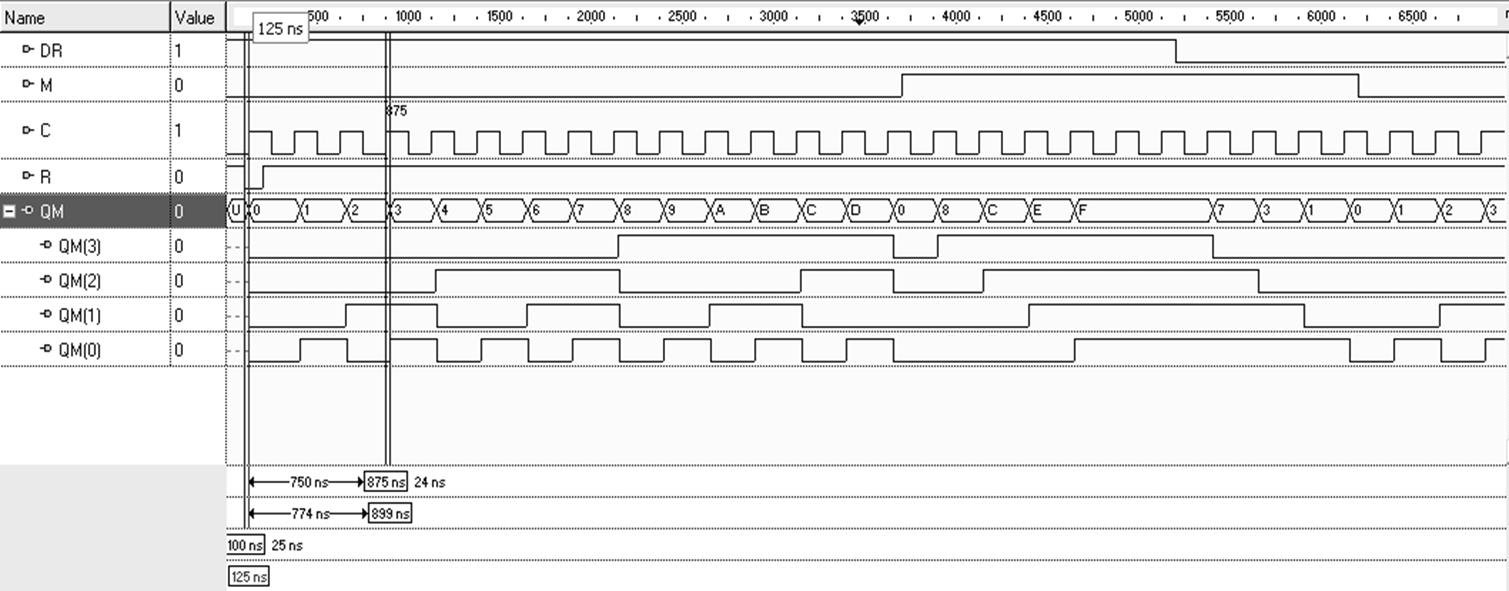

Рис. 17 Результаты верификации схемы с использованием мультиплексоров

Для реализации комбинационной части автомата на дешифраторах необходимо на их входы подавать значения аргументов функции возбуждения. Таким образом, на выходах дешифратора мы получим набор всех возможных конъюнкций этих аргументов. Остается лишь объединить нужные конъюнкции по схеме ИЛИ и мы получим необходимые функции возбуждения входов для JK-триггера.

Учитывая, что функция возбуждения зависит от 6 переменных необходимо спроектировать дешифратор 6->64. Обладая таким инструментом как язык VHDL, нам не составит труда спроектировать дешифратор на 64 выхода, но насколько громоздкий он получится и не эффективный в использовании. Поэтому вместо построения дешифратора 6-64 воспользуемся схемой наращивания размерности дешифраторов. В следствии такого решения нужно спроектировать дешифратор 4-16, что намного проще и реалистичнее и еще один вспомогательный дешифратор 2-4. На входы DC 2-4 подаются сигналы M и DR, а выходы этого дешифратора являются сигналами разрешения работы одного из дешифраторов декодирующих поля Q3, Q2, Q1, Q0 Т.к. при режиме М=0 (двоичный суммирующий счетчик по модулю 14) значение входа DR безразлично, то от одного дешифратора можно избавиться. Таким образом, вместо 64 выходов у нас получилось 48 дешифраторов, что значительно упрощает решение поставленной задачи. Еще одно упрощение: так как при режиме М=1 – регистр сдвига вправо, от входа DR зависит только старший триггер, поэтому выходы дешифратора, на вход разрешения которого идет сигнал M*DR, будем использовать только для старшего триггера.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.