Министерство образования и науки Российской Федерации

Федеральное агентство по образованию

Государственное образовательное учреждение

Высшего профессионального образования

Новосибирский государственный технический университет

Кафедра вычислительной техники

|

по дисциплине “Моделирование”

Факультет: АВТФ

Группа: АМ-411

Выполнил: Вагизов А.Р.

Вариант: ИВ3

Преподаватель: Шалагинов А.В. Дата сдачи:

Содержание.

1..... Постановка задачи. 2

2..... Условное графическое обозначение моделируемого узла. 2

3..... Таблица назначения выводов. 2

4..... Логическая таблица режимов работы элемента. 2

5..... Таблица реальных задержек. 2

6..... Описание работы проектируемого узла. 2

7..... Проектирование микросхемы К555ИВ3 в САПР DesignLab 8. 2

7.1.. УГО проектируемого узла. 2

7.2.. Схема замещения проектируемого узла. 2

7.3.. Текстовое SPICE-описание моделируемого узла. 2

7.4.. Содержимое файла описания внешних воздействий. 2

7.5.. Функциональное описание проектируемого узла с помощью примитивов LOGICEXP, PINDLY, и CONSTRAINT. 2

7.6.. Схема верификации иерархического символа. 2

7.7.. Результаты моделирования узла в пакете DesignLab 8. 2

7.8.. Оценка предельных скоростных (частотных) возможностей исследуемого узла. 2

8..... Проектирование микросхемы К555ИВ3 в САПР OrCAD 9.1. 2

8.1.. Иерархический символ, поддерживаемый схемой замещения. 2

8.2.. Иерархический символ, поддерживаемый поведенческой VHDL-моделью. 2

8.3.. Схема верификации иерархических символов. 2

8.4.. Результаты моделирования узла в пакете OrCAD 9.1. 2

9. Проектирование микросхемы К555ИВ3 в САПР Active-HDL 6.2. 2

9.1. УГО элемента К555ИВ3 в пакете Active-HDL 6.2. 2

9.2. Схема замещения К555ИВ3. 2

9.3. Схема верификации проектируемого элемента. 2

9.4.. Результаты моделирования узла в пакете Active HDL 6.2. 2

10... Выводы и личные впечатления. 2

Необходимо разработать цифровой узел, создать его структурные и поведенческие модели (на языках SPICE, DSL, VHDL, в пакетах DesignLab 8, OrCAD 9.1, Active-HDL 6.2). Затем провести имитационные эксперименты с разработанным узлом, целью которых является подтверждение работоспособности узла и проверка на соответствие его временных задержек требуемым.

Индивидуальное задание: Разработать приоритетный шифратор (кодер) – ИВ3 (зарубежный аналог - 147).

Было принято решение разработать реальный элемент К555ИВ3 – на элементной базе серии К555 (зарубежный аналог – 74LS147 – на базе серии 74LS).

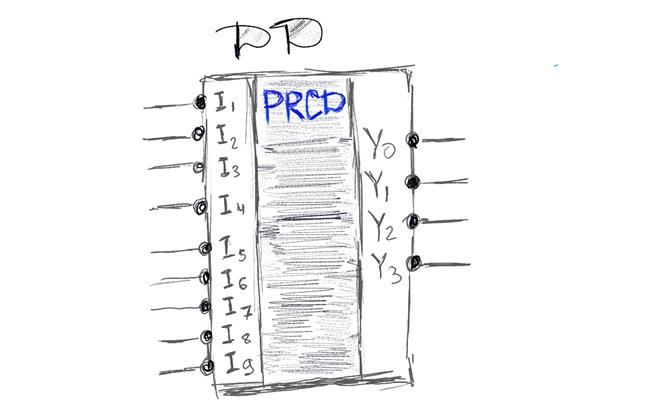

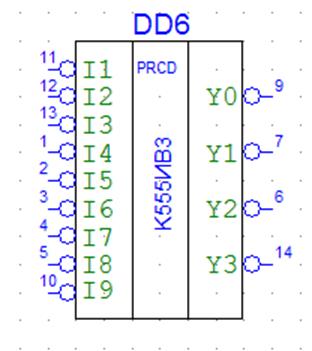

На рис.1

приведены условные графические обозначения (УГО) К555ИВ3, созданные в каждой из

САПР (систем автоматизированного проектирования): DesignLab

8, OrCAD 9.1, Active-HDL 6.2 соответственно:

На рис.1

приведены условные графические обозначения (УГО) К555ИВ3, созданные в каждой из

САПР (систем автоматизированного проектирования): DesignLab

8, OrCAD 9.1, Active-HDL 6.2 соответственно:

а). б). в).

Рис.1. УГО моделируемого компонента в пакетах DesignLab 8 (а), OrCAD 9.1 (б) и Active HDL 6.1 (в).

УГО моделируемого узла взято из книги [1].

Таблица 1. Выводы компонента К555ИВ3 и их назначение.

|

Номер вывода |

Название |

Функции вывода |

|

Входы |

||

|

11, 12, 13, 1, 2, 3, 4, 5, 10 |

I1, I2, I3, I4, I5, I6, I7, I8, I9 |

Девять входов, по которым генерируется выходной код. Т.к. у К555ИВ3 активные уровни сигналов – низкие (low - L), то входы I1-I9 на УГО показаны как инверсные. |

|

Выходы |

||

|

9, 7, 6, 14 |

Y0, Y1, Y2, Y3 |

Инверсные выходы кодера. В зависимости от номера активного сигнала на входе, на выходе формируется тот или иной двоично-десятичный код. |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.