Полученная модель получилась достаточно громоздкой, но я не придумал, как иначе можно реализовать разные задержки на тех или иных выходах в зависимости от того, как выходные сигналы переключаются относительно входных.

Теперь всё готово, осталось собрать схему верификации и протестировать элементы.

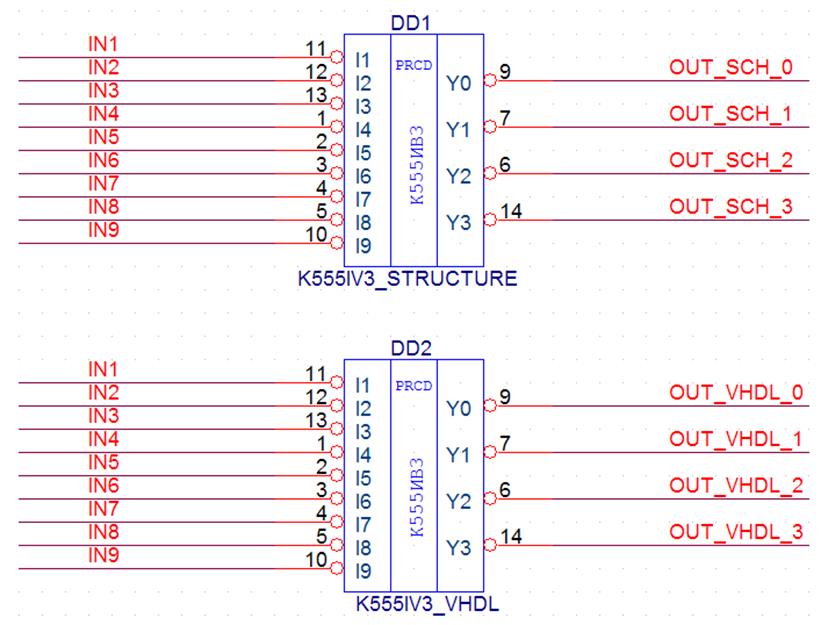

Рис. 19. Схема верификации элемента К555ИВ3 в пакете OrCad 9.1.

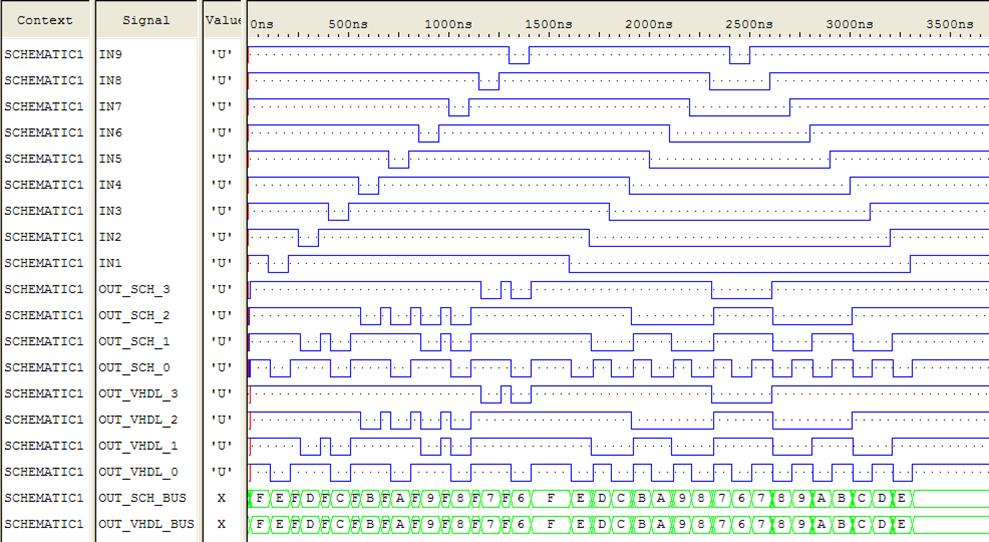

Рис. 20. Временная диаграмма работы проектируемого компонента.

На ВД на рис.20 показан эксперимент полностью. Рассмотрим более подробно все возможные ситуации, которые могут произойти в работе узла (как в п. 7.7):

1). На всех входах – высокий уровень напряжения (Н или 1), на какой-либо из входов поступает низкий уровень (т.е. активный уровень).

Пусть активным будет вход 5:

Рис. 21. Задержка распространения сигнала при переключении входа I5 c высокого уровня на низкий. Все остальные входы неактивны.

2). На всех входах, кроме одного – высокий уровень напряжения (1). И этот единственный вход также переключается в высокий уровень.

Рис. 22. Задержка распространения сигнала при переключении входа I2 c низкого уровня на высокий. Все остальные входы неактивны.

3). Активный уровень поступает на более приоритетный вход.

Рис. 23. Задержка распространения сигнала при переключении входа I4 высокого уровня на низкий и активных входах I1, I2 и I3.

4). «Снятие» активного уровня с более приоритетного входа при наличии активных уровней на менее приоритетных.

Рис. 24. Задержка распространения сигнала при переключении входа I8 c низкого уровня на высокий и активных менее приоритетных входах.

Временные диаграммы показывают идентичные временные задержки для элемента со схемой замещения и для элемента с VHDL-моделью.

Рис. 25. УГО проектируемого элемента в пакете Active HDL.

Рис. 26. Схема замещения элемента К555ИВ3 в пакете ActiveHDL.

Рис. 27. Схема верификации проектируемого узла в пакете ActiveHDL 6.2

На данном рисунке за элементом с позиционным обозначением DD1 закреплена схема замещения, а за элементом DD2 – VHDL-модель. VHDL-модель, используемая в данном пакете полностью аналогична модели в пакете OrCAD за исключением названия архитектуры элемента (architecture K555IV3_VHDL of K555IV3_VHDL вместо ARCHITECTURE BEHAVIOR OF K555IV3_VHDL).

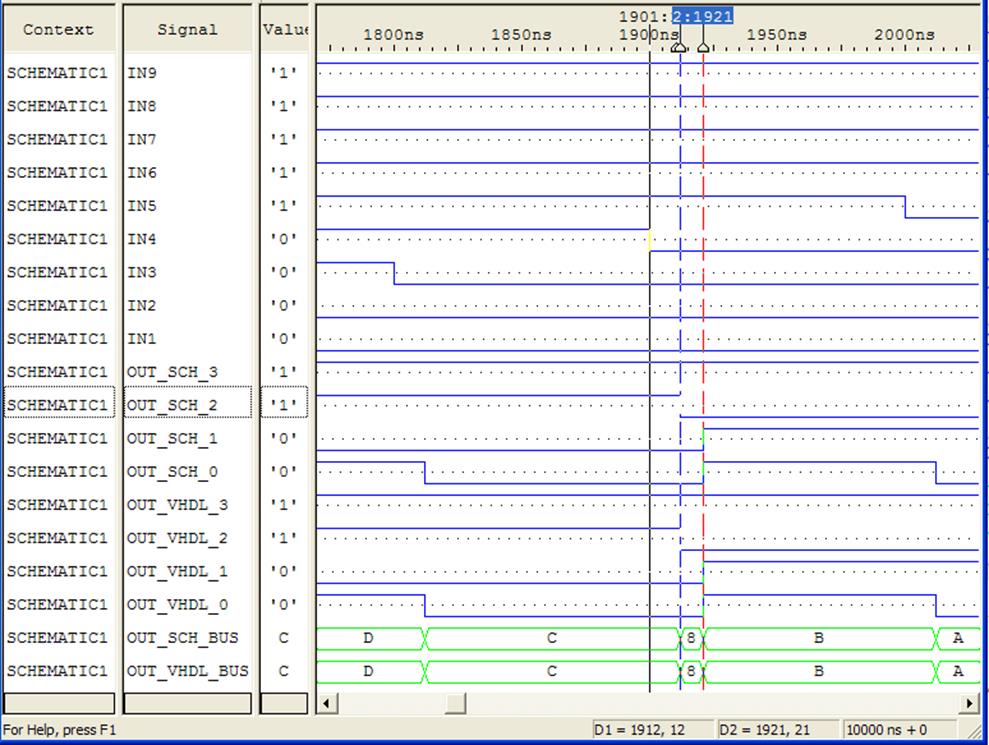

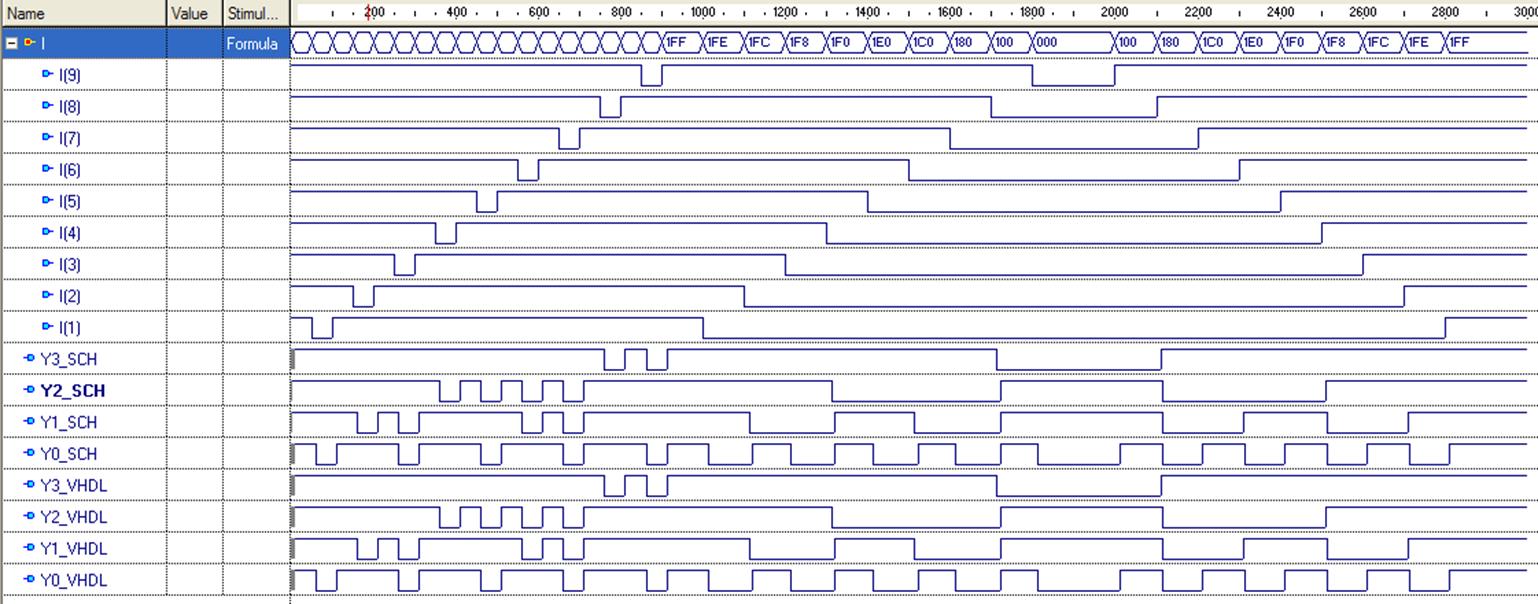

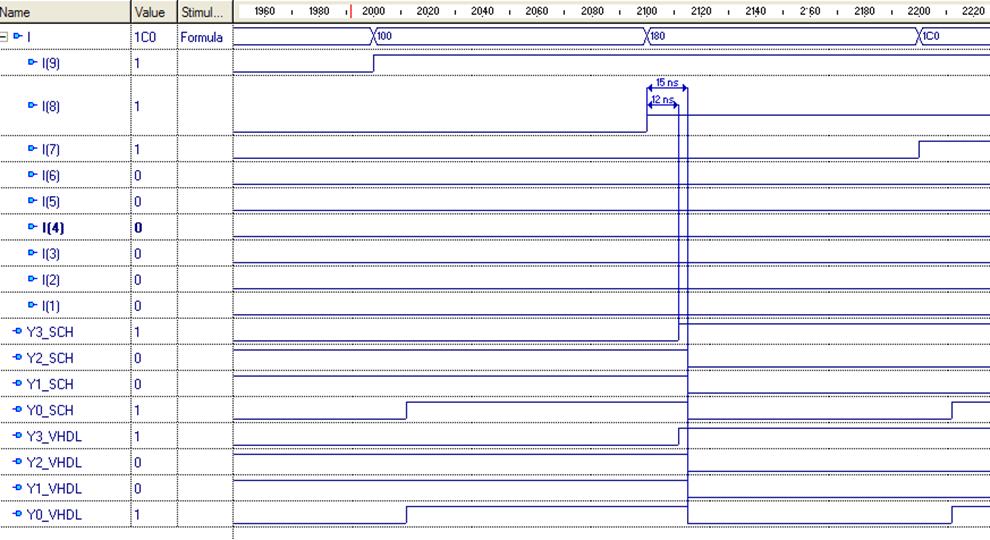

Рис. 28. Временная диаграмма работы проектируемого компонента.

На полученной ВД можно увидеть эксперимент полностью. Сам эксперимент аналогичен тестам компонента в других САПР.

Сигналы I(9) – I(1) – входные сигналы

Y3_SCH – Y0_SCH – выходы элемента, поддерживаемого схемой замещения

Y3_VHDL – Y0_VHDL - выходы элемента, поддерживаемого VHDL-моделью.

Как и в других САПР, рассмотрим некоторые моменты более подробно:

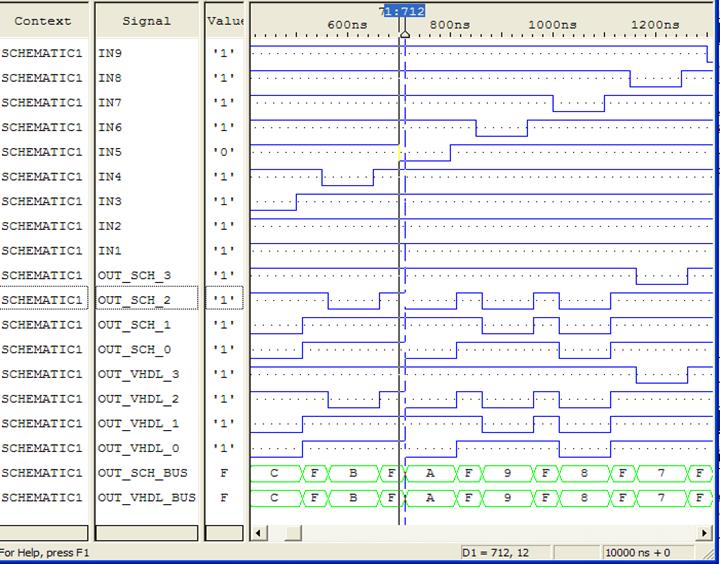

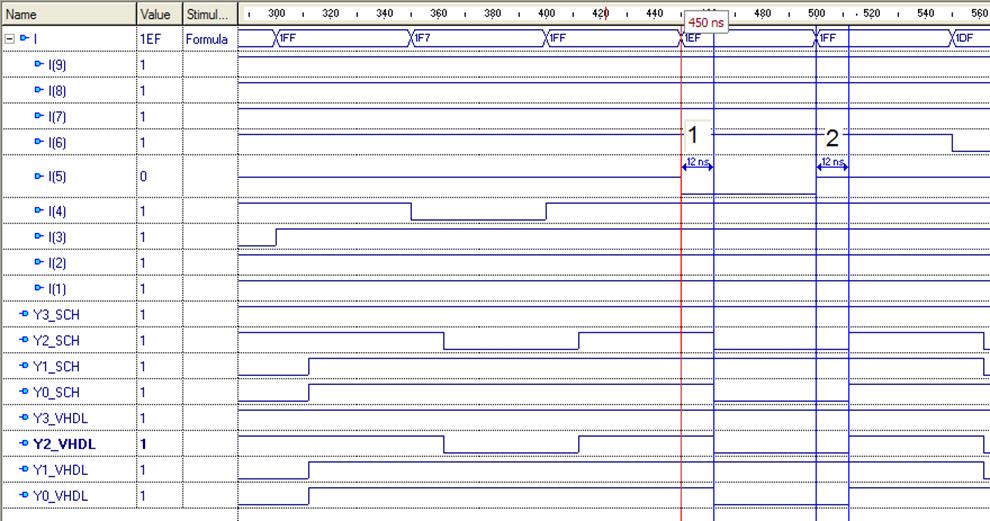

1). На всех входах – высокий уровень напряжения (Н или 1), на какой-либо из входов поступает низкий уровень (т.е. активный уровень).

2). На всех входах, кроме одного – высокий уровень напряжения (1). И этот единственный вход также переключается в высокий уровень.

Рис. 29. Задержка распространения сигнала при переключении входа I5 c высокого уровня на низкий (1) и наоборот (2). Все остальные входы неактивны.

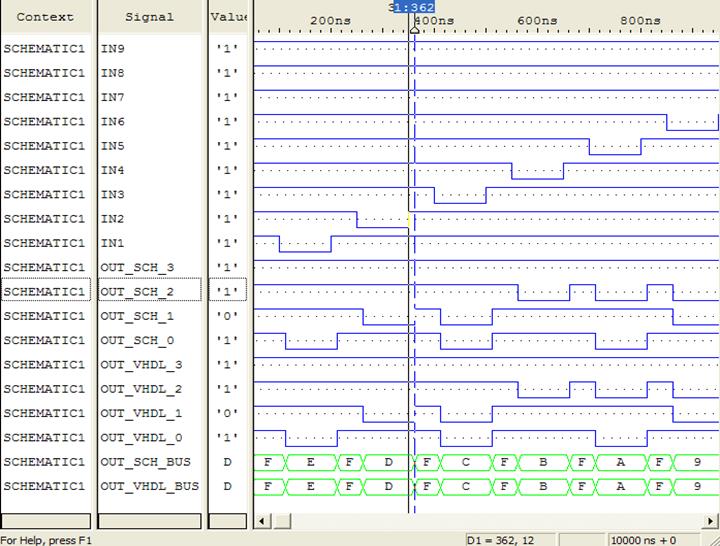

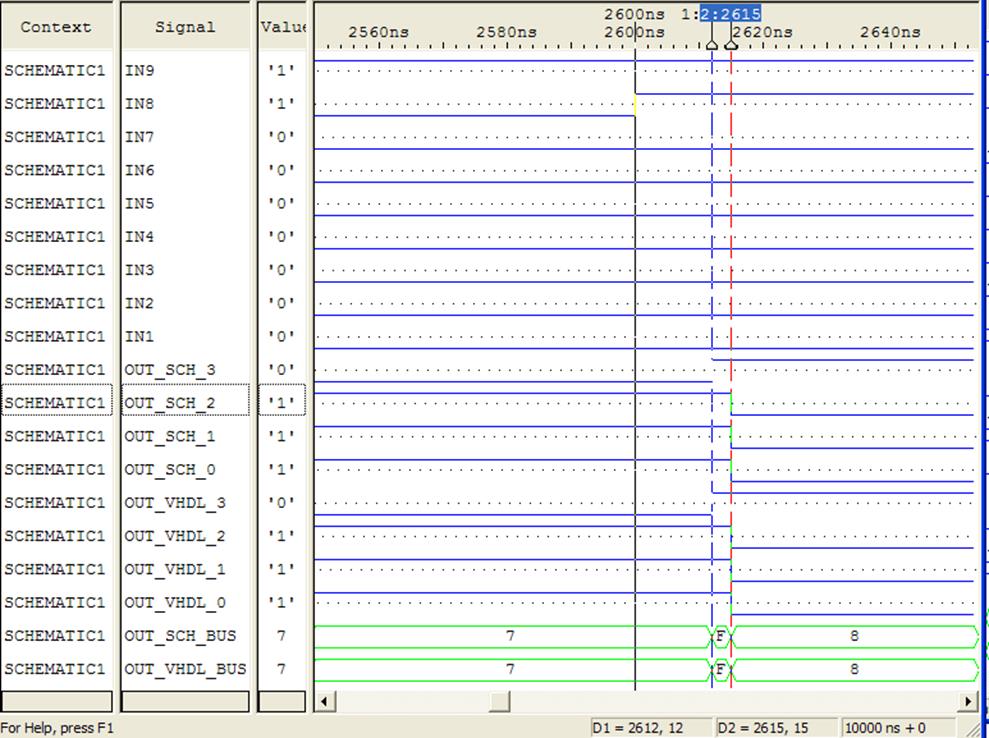

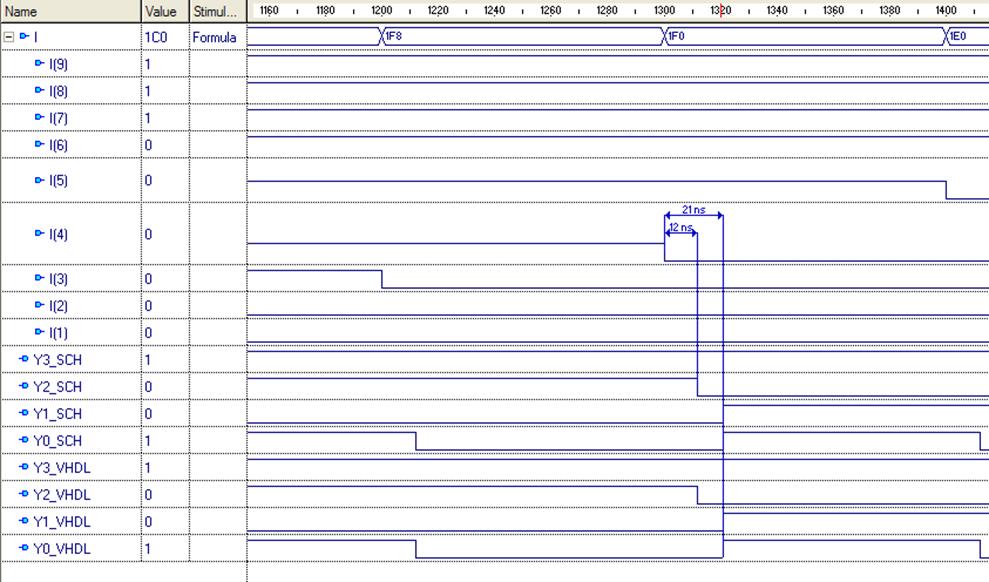

3). Активный уровень поступает на более приоритетный вход.

Рис. 30. Задержка распространения сигнала при переключении входа I4 высокого уровня на низкий и активных входах I1, I2 и I3.

4). «Снятие» активного уровня с более приоритетного входа при наличии активных уровней на менее приоритетных.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.