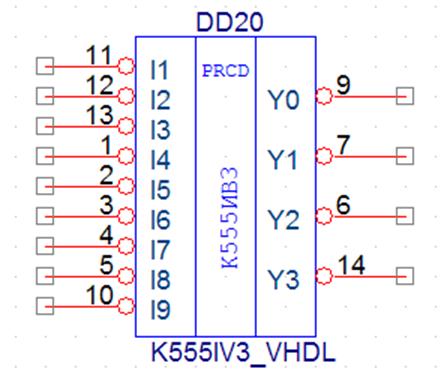

Рис. 18. УГО проектируемого символа, поддерживаемого VHDL-моделью в пакете OrCad 9.1

Ниже приведена VHDL-модель, закреплённая за этим символом:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE work.orcad_prims.all;

ENTITY K555IV3_VHDL IS --описание интерфейса модели

PORT( --перечисление входных и выходных портов узла

I1 : IN std_logic;

I2 : IN std_logic;

I3 : IN std_logic;

I4 : IN std_logic;

I5 : IN std_logic;

I6 : IN std_logic;

I7 : IN std_logic;

I8 : IN std_logic;

I9 : IN std_logic;

Y0 : OUT std_logic;

Y1 : OUT std_logic;

Y2 : OUT std_logic;

Y3 : OUT std_logic;

);

END K555IV3_VHDL;

ARCHITECTURE BEHAVIOR OF K555IV3_VHDL IS --начало описания архитектуры элемента

BEGIN

process (I1,I2,I3,I4,I5,I6,I7,I8,I9) --определение процесса, реагирующего на изменение

--какого-либо из входных сигналов

variable Y_INT_NEW: std_logic_vector (3 downto 0); --вспомогательные переменные, исполь-

variable Y_INT_PREV: std_logic_vector (3 downto 0); --зуются для получения нового и запоми-

--нания старого значения на выходе.

--Это нужно для определения того, как

--переключался выход – с 0 на 1 или с 1 на 0

begin

--если зашли в процесс – значит произошло переключение какого-либо из входов, а, значит,

--и переключение каких-то выходов (т.к. входы имеют разный приоритет и каждому

--входу соответствует своя уникальная комбинация на выходе).

Y_INT_PREV:=Y_INT_NEW; --запоминание предыдущих значений на выходе

if (I1='1' and I2='1' and I3='1' and I4='1' and I5='1' and I6='1' and I7='1' and I8='1' and I9='1') then

Y_INT_NEW:="1111"; --если ни один из входов не активен – на выходах

end if; --напряжение высокого уровня

--каждому входному сигналу соответствует определённая комбинация на выходах

-- 0 – активный уровень, I9 – вход с наибольшим приоритетом.

if I9='0' Then --если активен вход I9 – «выставить» на выход "0110"

Y_INT_NEW:="0110"; --и т.д.

elsif I8='0' Then

Y_INT_NEW:="0111";

elsif I7='0' Then

Y_INT_NEW:="1000";

elsif I6='0' Then

Y_INT_NEW:="1001";

elsif I5='0' Then

Y_INT_NEW:="1010";

elsif I4='0' Then

Y_INT_NEW:="1011";

elsif I3='0' Then

Y_INT_NEW:="1100";

elsif (I2='0' ) Then

Y_INT_NEW:="1101";

elsif I1='0' Then

Y_INT_NEW:="1110";

end if;

------------------------------------------------------------------------------

--выход Y0

--если выход Y0 переключился с 0 на 1 вследствие снятия активного уровня с какого-либо из

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.