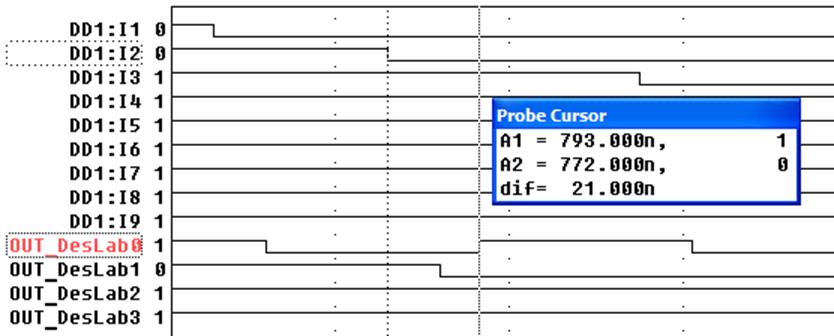

Конечно, нигде не указано, что 74LS147 в DesignLab’е работает в соответствии с фирменной документацией, но уж если разработчики макромодели для этого элемента предусмотрели одну их задержек в режиме противофазы (рис. 7), то почему бы не сделать и вторую задержку?

В разработанной макромодели этот недостаток исправлен.

Рис. 7. Задержка распространения сигнала при переключении входа I2 c высокого уровня на низкий и активном входе I1.

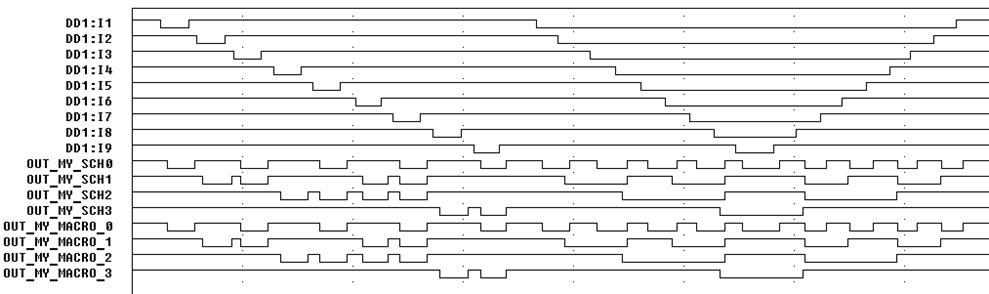

Итак, теперь можно привести результаты моделирования собственных компонентов. Стоит отметить, что было решено на временных диаграммах (ВД) не показывать работу иностранного аналога по вышеописанным причинам.

Рис. 8. Временная диаграмма работы проектируемого компонента.

На полученной ВД:

I1 – I9 – сигналы, подаваемые на вход кодеров (на схеме пробники установлены перед входами элемента DD1, но это не должно путать: на входы элементов DD1 и DD2 подаются совершенно одинаковые сигналы).

OUT_MY_SCH[3-0] – выходы символа, поддерживаемого схемой замещения.

OUT_MY_MACRO_[3-0] – выходы символа, поддерживаемого макромоделью.

На рис.8 показан полный эксперимент, полученные результаты показывают, что задержки «заложенные» в макромодели идентичны задержкам, измеренным на схеме замещения.

Рассмотрим более подробно следующие случаи:

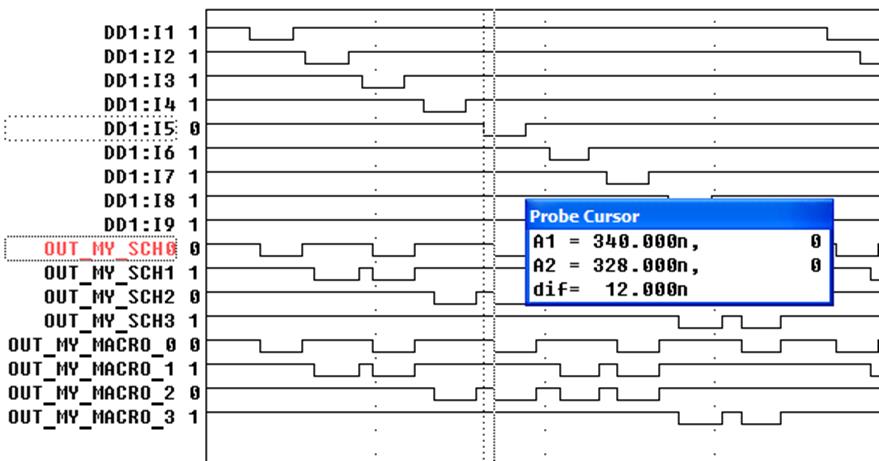

1). На всех входах – высокий уровень напряжения (Н или 1), на какой-либо из входов поступает низкий уровень (т.е. активный уровень).

Пусть активным будет вход 5:

Рис. 9. Задержка распространения сигнала при переключении входа I5 c высокого уровня на низкий. Все остальные входы неактивны.

На данной ВД видно, что по приходу низкого уровня сигнала на вход I5, выходные сигналы под номерами 0 и 2 переключились в 0, что соответствует комбинации 1010 (это инвертированная пятёрка – значит, всё верно). Переключение выходных сигналов относительно входных произошло в фазе, поэтому задержка должна составлять 12 нс. Так оно и есть.

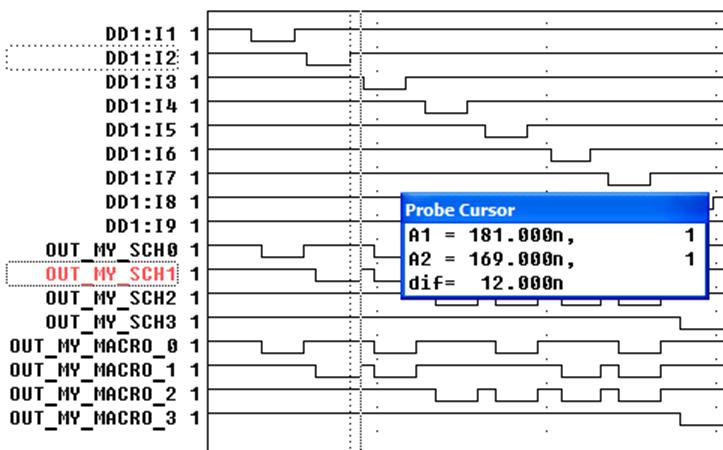

2). На всех входах, кроме одного – высокий уровень напряжения (1). И этот единственный вход также переключается в высокий уровень.

Рис. 10. Задержка распространения сигнала при переключении входа I2 c низкого уровня на высокий. Все остальные входы неактивны.

До переключения входа I2 с 0 на 1 значение выходов было 1101, что соответствует инверсной двойке. Переключение выходных сигналов относительно входных произошло в фазе (а именно, выход под номером 1 переключился с 0 на 1), поэтому задержка должна составлять 12 нс.

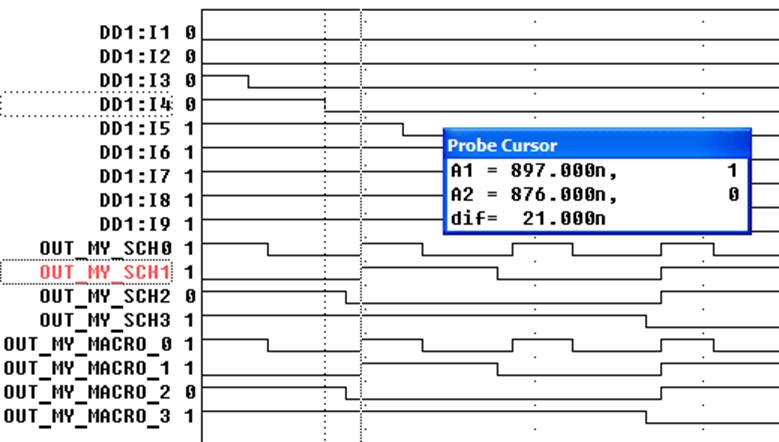

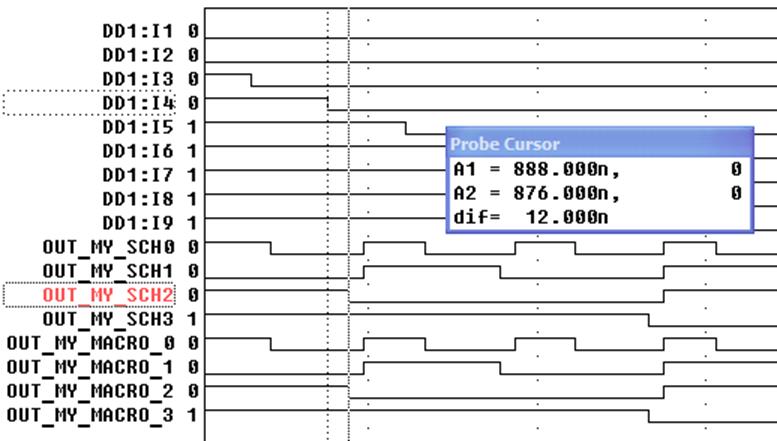

3). Активный уровень поступает на более приоритетный вход.

а).

б).

Рис. 11. Задержка распространения сигнала при переключении входа I4 высокого уровня на низкий и активных входах I1, I2 и I3.

В данном случае до прихода активного уровня на вход I4 на выходах была комбинация 1100, т.к. самым старшим активным входом был третий вход. Поступление активного уровня на вход I4 «превращает» выходную комбинацию в 1011. При этом два младших разряда переключаются из 0 в 1 (т.е. в противофазе относительно входного) за 21 нс (рис. 11, а), а третий разряд – из 1 в 0 (в фазе) за 12 нс (рис. 11, б). Задержки идентичны табличным.

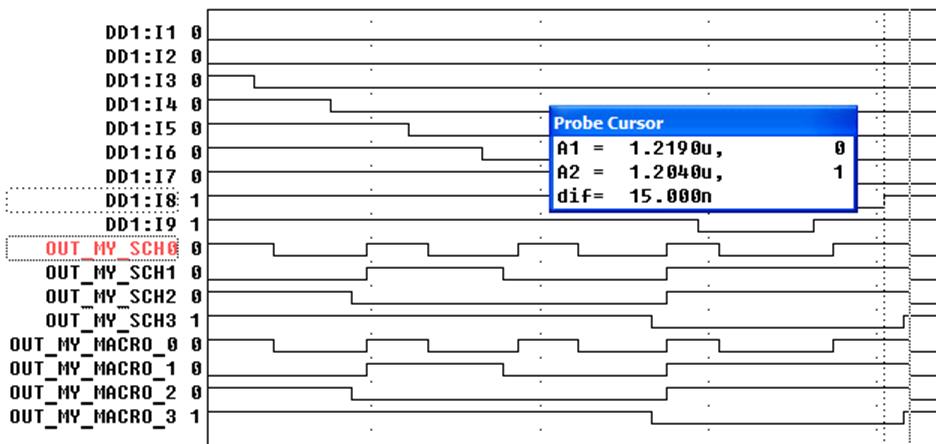

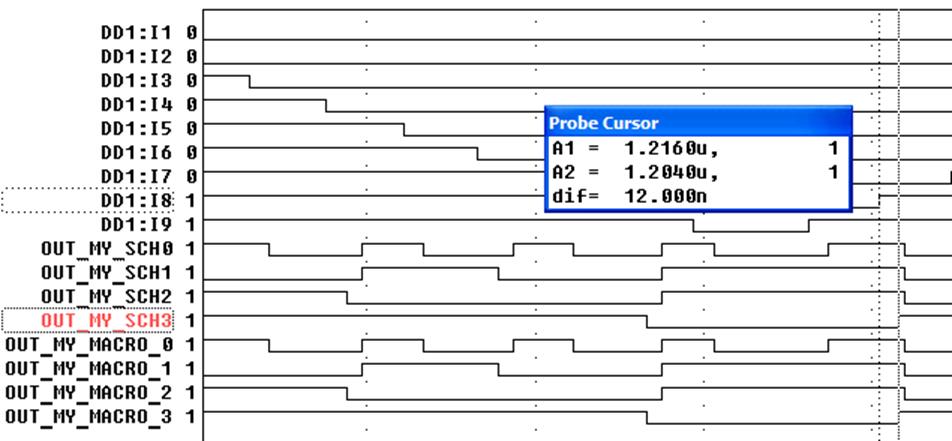

4). «Снятие» активного уровня с более приоритетного входа при наличии активных уровней на менее приоритетных.

а).

б).

Рис. 12. Задержка распространения сигнала при переключении входа I8 c низкого уровня на высокий и активных менее приоритетных входах.

Данная ситуация с точностью до наоборот аналогична предыдущей. Комбинация 0111 меняется на 1000.

Таким образом, мы рассмотрели все возможные ситуации, которые могут произойти в работе узла.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.