+* логические выражения для выходных узлов без учёта задержек:

+ D = { IN8 & IN9 }

+ C = { ~(D & (IN4BAR | IN5BAR | IN6BAR | IN7BAR)) }

+ B = { ~(D & ((IN2BAR & IN4 & IN5) |

+ (IN3BAR & IN4 & IN5) | IN6BAR | IN7BAR)) }

+ A = { ~(IN9BAR | D & ((IN1BAR & IN2 & IN4 & IN6) |

+ (IN3BAR & IN4 & IN6) | (IN5BAR & IN6) | IN7BAR)) }

+

+

UIV3DLY PINDLY (4,0,9) DPWR DGND *начало примитива PINDLY

*примитив имеет 4 пути (входа), для которых вычисляется задержка:

+ A B C D

+

* примитив имеет три внутренних узла, от которых зависит эта задержка:

+ IN1 IN2 IN3 IN4 IN5 IN6 IN7 IN8 IN9

+

+ A_O B_O C_O D_O * имя выходных узлов примитива PINDLY

+ IO_LS * стандартная модель вход/выход

+ MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL}

+

+ BOOLEAN: * секция определяет промежуточные переменные,

+ *которые используются для вычисления задержек

*+какой-либо входной сигнал переключился с 0 на 1:

+ ANY_INPUT_CHANGED_LH={CHANGED_LH (IN1, 0) | CHANGED_LH (IN2, 0) | CHANGED_LH (IN3, 0) |

+CHANGED_LH (IN4, 0) | CHANGED_LH (IN5, 0) | CHANGED_LH (IN6, 0) | CHANGED_LH (IN7, 0) | CHANGED_LH (IN8, 0) | CHANGED_LH (IN9, 0)}

+

+* какой-либо входной сигнал переключился с 1 на 0:

+ ANY_INPUT_CHANGED_HL={CHANGED_HL (IN1, 0) | CHANGED_HL (IN2, 0) | CHANGED_HL (IN3, 0) | CHANGED_HL (IN4, 0) |

+ CHANGED_HL (IN5, 0) | CHANGED_HL (IN6, 0) | CHANGED_HL (IN7, 0) | CHANGED_HL (IN8, 0) | CHANGED_HL (IN9, 0) }

*+

+ PINDLY:

+ A_O B_O C_O D_O = {

+ CASE (

+ *если входной сигнал переключился с 0 на 1 и выходной – тоже с 0 на 1, то задержка 12 нс:

+ ANY_INPUT_CHANGED_LH & TRN_LH, DELAY(-1,12NS,18NS),

+ *если входной сигнал переключился с 0 на 1, а выходной – с 1 на 0, то задержка 15 нс:

+ ANY_INPUT_CHANGED_LH & TRN_HL, DELAY(-1,15NS,18NS),

+ *если входной сигнал переключился с 1 на 0, а выходной – с 0 на 1, то задержка 12 нс:

+ ANY_INPUT_CHANGED_HL & TRN_LH, DELAY(-1,21NS,18NS),

+ *если входной сигнал переключился с 1 на 0 и выходной – тоже с 1 на 0, то задержка 12 нс:

+ ANY_INPUT_CHANGED_HL & TRN_HL, DELAY(-1,12NS,18NS),

+ DELAY(-1,21NS,33NS)

+ )

+ }

*

.ENDS

*

*$

Т.к., шифратор – комбинационная схема, то в модели для него примитив CONSTRAINT не нужен – в схеме нет триггеров, для которых необходимы предустановка и удержание данных на входах.

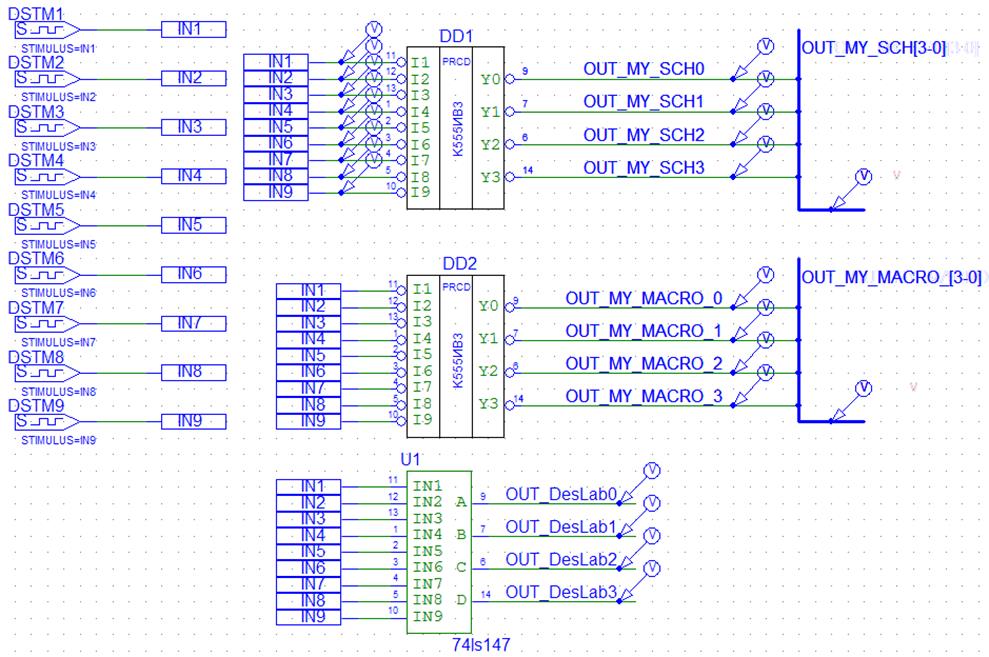

Итак, схема замещения и макромодель получены, теперь можно производить верификацию шифратора. Схема верификации приведена на рис. 5.

Рис. 5. Схема верификации иерархического символа.

На данной схеме элемент с позиционным обозначением DD1 – иерархический символ K555ИВ3, поддерживаемый схемой замещения, а DD2 – поддерживаемый макромоделью.

Также на схеме присутствует зарубежный аналог шифратора К555ИВ3.

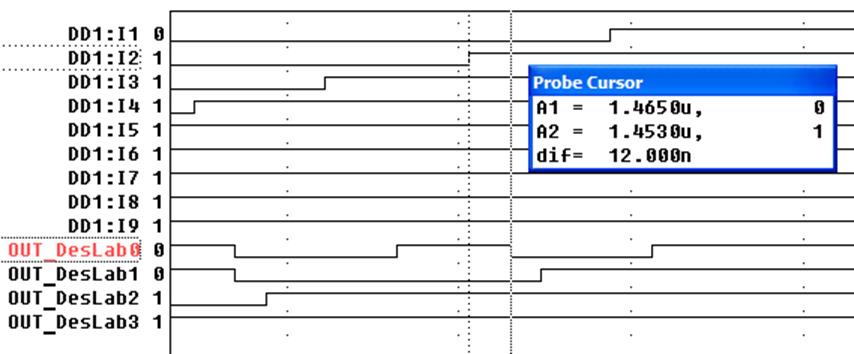

Прежде чем тестировать «самодельный» элемент, хочется отметить не совсем корректную работу иностранного аналога проектируемого узла – кодера 74LS147.

Дело в том, что в случае, когда входной сигнал переключается с низкого уровня на высокий, а какой-либо выход вследствие этого переключается с высокого на низкий (т.е. выход переключается относительно входа в противофазе), то задержка такого изменения сигнала на выходе должна равняться 15 нс (см. п. 5 или Приложение 1). А она составляет 12 нс:

Рис. 6. Задержка распространения сигнала при переключении входа I2 c низкого уровня на высокий и активном входе I1.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.