Новосибирский государственный технический университет

Кафедра ВТ

Курсовая работа по дисциплине «Моделирование»

Тема: «Проектирование цифрового узла в САПР DesignLab 8.0 и OrCAD 9.1»

Работа выполнена: Работа проверена: Студент: Баркалов Д.С. Преподаватель: Шалагинов А. В.

Группа: АМ-210

Факультет: АВТ

Новосибирск 2005г.

1. Постановка задачи. 3

2. Условное графическое обозначение (УГО) проектируемого узла. 3

3. Таблица назначения выводов. 3

4. Логическая таблица режимов работы.. 4

5. Таблица реальных задержек распространения. 4

6. Описание работы проектируемого узла. 5

7. Моделирование узла в пакете DesignLab 8.0. 5

7.1. Условное графическое изображение проектируемого узла. 5

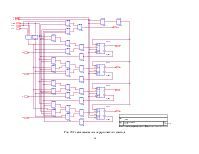

7.2. Схема замещения проектируемого узла. 5

7.3. Текстовое SPICE-описание моделируемого узла. 8

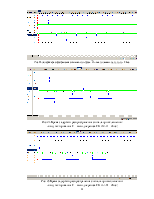

7.4. Диаграммы входных сигналов. 10

7.5. Схема верификации иерархического символа. 11

7.6. Результаты моделирования проектируемого узла. 11

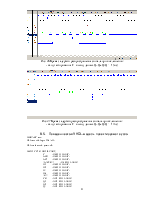

7.7. Оценка предельных скоростных (частотных) возможностей. 14

исследуемого узла. 14

7.8. Функциональное описание проектируемого и оформление его в. 15

виде макромодели. 15

7.9. Схема верификации символа с подключённой к нему макромоделью.. 17

8. Моделирование узла в пакете OrCad 9.1. 19

8.1. Условное графическое обозначение проектируемого узла. 19

8.2. Принципиальная схема замещения проектируемого узла. 19

8.3. Схема верификации иерархического символа. 21

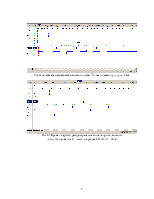

8.4. Результаты моделирования узла. 21

8.5. Поведенческая VHDL-модель проектируемого узла. 23

8.6. Верификация поведенческой VHDL-модели, подключённой к иерархическому символу. 25

9. Выводы и личные впечатления. 28

9.1. Краткая характеристика и сравнительный анализ использованных пакетов моделирования. 28

9.2. Личные впечатления. 29

10. Список использованной литературы.. 31

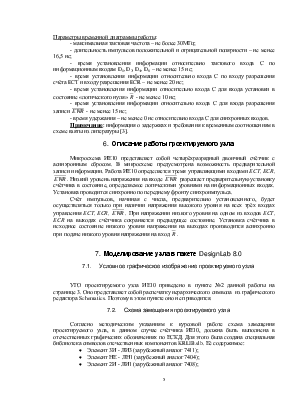

Вариантом к настоящей курсовой работе задан цифровой узел ИЕ10 – четырёхразрядный двоичный счётчик с асинхронной установкой в состояние логического нуля. Требуется создать его структурные и поведенческие модели (на языках SPICE, DSL, VHDL и SimCode, в пакетах DesignLab 8, OrCAD 9.1, Active-HDL 6.1 или PCAD 2002) и провести имитационные эксперименты с разработанным узлом, с целью подтверждения работоспособности узла, определения максимально допустимой частоты его работы и соответствия его временных задержек требуемым.

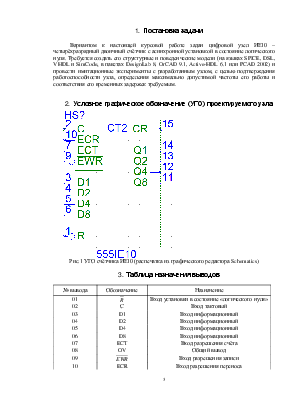

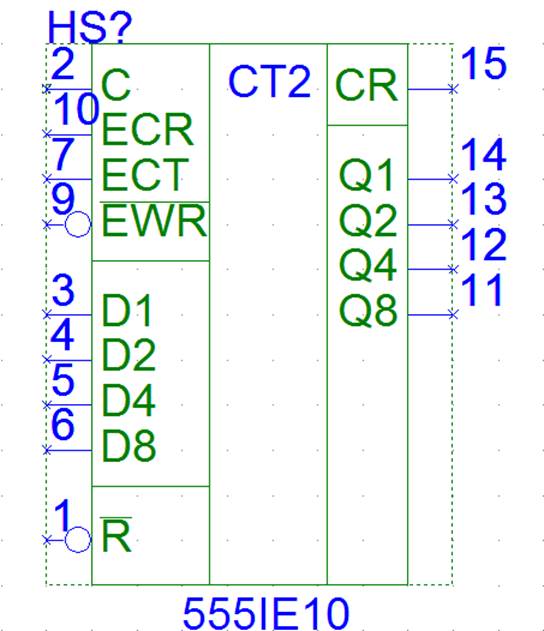

Рис.1 УГО счётчика ИЕ10 (распечатка из графического редактора Schematics)

|

№ вывода |

Обозначение |

Назначение |

|

01 |

|

Вход установки в состояние «логического нуля» |

|

02 |

С |

Вход тактовый |

|

03 |

D1 |

Вход информационный |

|

04 |

D2 |

Вход информационный |

|

05 |

D4 |

Вход информационный |

|

06 |

D8 |

Вход информационный |

|

07 |

ECT |

Вход разрешения счёта |

|

08 |

OV |

Общий вывод |

|

09 |

|

Вход разрешения записи |

|

10 |

ECR |

Вход разрешения переноса |

|

11 |

Q8 |

Выход третьего разряда |

|

12 |

Q4 |

Выход второго разряда |

|

13 |

Q2 |

Выход первого разряда |

|

14 |

Q1 |

Выход нулевого разряда |

|

15 |

CR |

Выход переноса |

|

16 |

Ucc |

Вывод питания от источника напряжения |

Табл. 1 Назначение выводов

|

Режим |

Входы |

Выходы |

||||||

|

|

С |

ECT |

ECR |

|

Dn |

Qn |

CR |

|

Сброс |

0 |

X |

X |

X |

X |

X |

0 |

0 |

Параллельная загрузка |

1 |

↑ |

X |

X |

0 |

0 |

0 |

0 |

1 |

↑ |

X |

X |

0 |

1 |

1 |

1 |

|

Счёт |

1 |

↑ |

1 |

1 |

1 |

X |

Счёт |

1 |

Хранение |

1 |

X |

0 |

X |

1 |

X |

Qn |

1* |

1 |

X |

X |

0 |

1 |

X |

Qn |

1* |

|

Табл. 2 Режимы работы

|

Примечания: 0 – низкий уровень; 1 – высокий уровень; X – неопределенное состояние (результат на выходе не зависит от этого значения); ↑ - переход сигнала из состояния «логического 0» в состояние «логической 1»; 1*- клетки таблицы означают, что значение на этом выходе зависит от значения на выходе Qn; |

Табл. 3 Примечания

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.