Рис. 24 Время задержки распространения сигнала при включении:

- вход тактирования C – выход переноса CR (0->1) – 23нс;

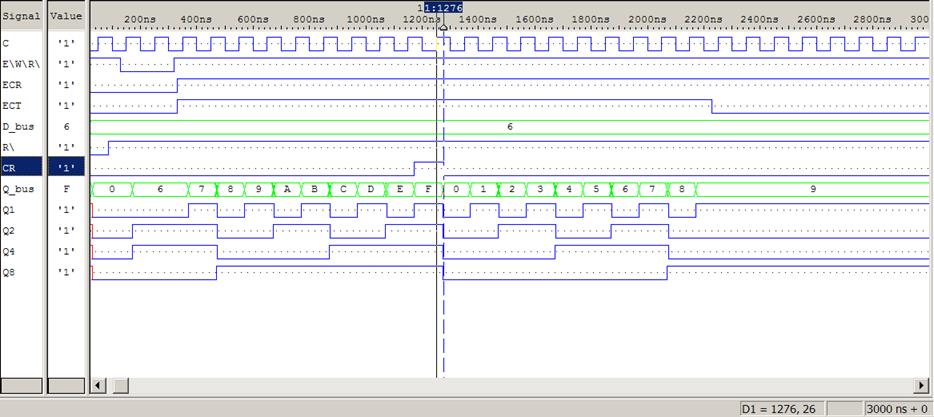

Рис. 25Время задержки распространения сигнала при выключении:

- вход тактирования C – выход переноса CR (1->0) – 26нс;

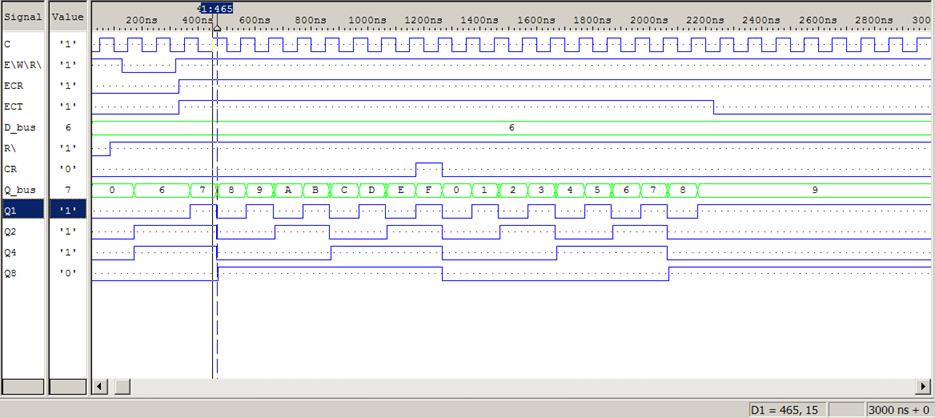

Рис. 26 Время задержки распространения сигнала при выключении:

- вход тактирования C – выход данных Q8,Q4,Q2,Q1 – 15нс;

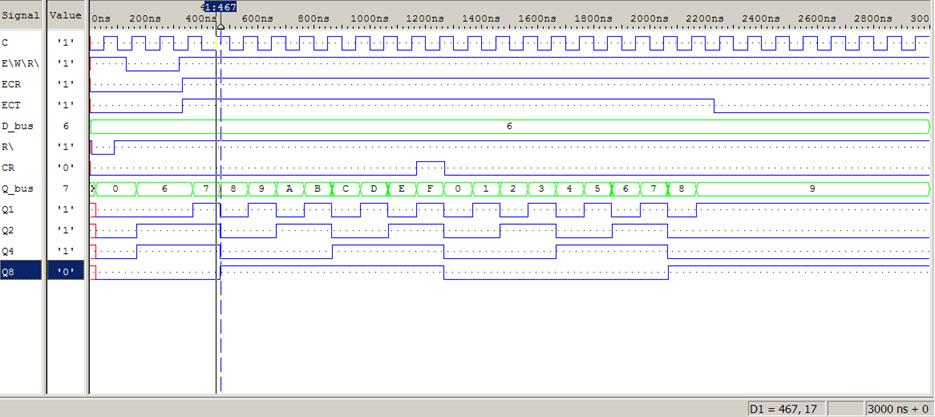

Рис. 27 Время задержки распространения сигнала при включении:

- вход тактирования C – выход данных Q8,Q4,Q2,Q1 – 17нс;

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE work.orcad_prims.all;

ENTITY CTR_HB1 IS PORT(

C : IN STD_LOGIC;

ECR : IN STD_LOGIC;

ECT : IN STD_LOGIC;

\E\\W\\R\\\ : IN STD_LOGIC;

D1 : IN STD_LOGIC;

D2 : IN STD_LOGIC;

D4 : IN STD_LOGIC;

D8 : IN STD_LOGIC;

\R\\\ : IN STD_LOGIC;

CR : OUT STD_LOGIC;

Q1 : OUT STD_LOGIC;

Q2 : OUT STD_LOGIC;

Q4 : OUT STD_LOGIC;

Q8 : OUT STD_LOGIC);

END CTR_HB1;

ARCHITECTURE model OF CTR_HB1 IS

SIGNAL L1 : std_logic;

SIGNAL L2 : std_logic;

SIGNAL L3 : std_logic;

SIGNAL L4 : std_logic;

SIGNAL L5 : std_logic;

SIGNAL L6 : std_logic;

SIGNAL L7 : std_logic;

SIGNAL L8 : std_logic;

SIGNAL L9 : std_logic;

SIGNAL L10 : std_logic;

SIGNAL L11 : std_logic;

SIGNAL L12 : std_logic;

SIGNAL L13 : std_logic;

SIGNAL L14 : std_logic;

SIGNAL L15 : std_logic;

SIGNAL L16 : std_logic;

SIGNAL L17 : std_logic;

SIGNAL L18 : std_logic;

SIGNAL L19 : std_logic;

SIGNAL L20 : std_logic;

SIGNAL N1 : std_logic;

SIGNAL N2 : std_logic;

SIGNAL N3 : std_logic;

SIGNAL N4 : std_logic;

SIGNAL N5 : std_logic;

SIGNAL N6 : std_logic;

BEGIN

N1 <= ( ECT AND \E\\W\\R\\\ AND ECR ) AFTER 0 ns;

N2 <= ( N3 AND N4 AND N5 AND N6 ) AFTER 7 ns;

CR <= ( ECR AND N2 ) AFTER 2 ns;

L1 <= NOT ( \E\\W\\R\\\ );

L2 <= ( \E\\W\\R\\\ AND N3 );

L3 <= ( L2 XOR N1 );

L4 <= ( L1 AND D1 );

L5 <= ( L3 OR L4 );

L6 <= ( \E\\W\\R\\\ AND N4 );

L7 <= ( N1 AND N3 );

L8 <= ( L6 XOR L7 );

L9 <= ( L1 AND D2 );

L10 <= ( L8 OR L9 );

L11 <= ( \E\\W\\R\\\ AND N5 );

L12 <= ( N1 AND N3 AND N4 );

L13 <= ( L11 XOR L12 );

L14 <= ( L1 AND D4 );

L15 <= ( L13 OR L14 );

L16 <= ( \E\\W\\R\\\ AND N6 );

L17 <= ( N1 AND N3 AND N4 AND N5 );

L18 <= ( L16 XOR L17 );

L19 <= ( L1 AND D8 );

L20 <= ( L18 OR L19 );

DQFFC_14 : ORCAD_DQFFC

GENERIC MAP (trise_clk_q=>10 ns, tfall_clk_q=>8 ns)

PORT MAP (q=>N3 , d=>L5 , clk=>C , cl=>\R\\\ );

DQFFC_15 : ORCAD_DQFFC

GENERIC MAP (trise_clk_q=>10 ns, tfall_clk_q=>8 ns)

PORT MAP (q=>N4 , d=>L10 , clk=>C , cl=>\R\\\ );

DQFFC_16 : ORCAD_DQFFC

GENERIC MAP (trise_clk_q=>10 ns, tfall_clk_q=>8 ns)

PORT MAP (q=>N5 , d=>L15 , clk=>C , cl=>\R\\\ );

DQFFC_17 : ORCAD_DQFFC

GENERIC MAP (trise_clk_q=>10 ns, tfall_clk_q=>8 ns)

PORT MAP (q=>N6 , d=>L20 , clk=>C , cl=>\R\\\ );

Q1 <= ( N3 ) AFTER 7 ns;

Q2 <= ( N4 ) AFTER 7 ns;

Q4 <= ( N5 ) AFTER 7 ns;

Q8 <= ( N6 ) AFTER 7 ns;

END model;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.