+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD77_3 $N_0015 D4 $N_0029 $G_DPWR $G_DGND 555LI1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD78_4 EWR $N_0006 $N_0030 $G_DPWR $G_DGND 555LI1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD79_1 $N_0021 $N_0019 CR $G_DPWR $G_DGND 555LI1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD80_2 EWR $N_0022 $N_0031 $G_DPWR $G_DGND 555LI1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD81_3 $N_0031 $N_0020 $N_0023 $G_DPWR $G_DGND 555LP5 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD82_3 $N_0020 $N_0022 $N_0024 $G_DPWR $G_DGND 555LI1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD83_5 $N_0009 $N_0022 $G_DPWR $G_DGND 555LN1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD84_3 $N_0020 $N_0002 $N_0022 $N_0026 $G_DPWR $G_DGND 555LI3

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD85_4 $N_0002 $N_0022 $N_0032 $G_DPWR $G_DGND 555LI1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD86_1 $N_0033 $N_0032 $N_0034 $G_DPWR $G_DGND 555LI1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD87_2 $N_0004 $N_0020 $N_0033 $G_DPWR $G_DGND 555LI1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD88_4 $N_0030 $N_0034 $N_0028 $G_DPWR $G_DGND 555LP5 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_U3 C ECR ECT R EWR D1 D2 D3 D4 QQ1 QQ2 QQ3 QQ4 CRR $G_DPWR $G_DGND

+ 74161 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

Файл описания внешних воздействий ctr_schema.stl содержит информацию о месте хранения файла с внешними воздействиями, а также времени его создания и версии программы, с помощью которой он создан.

* C:\MSim_8\Projects\CourseWork\ctr_schema.stl written on Fri Sep 23 11:23:05 2005

* by Stimulus Editor -- Serial Number: 100617 -- Version 8.0

;!Stimulus Get

;! C Digital ECR Digital ECT Digital EWR Digital D1 Digital D2 Digital D3 Digital D4 Digital R Digital

;!Ok

;!Plot Axis_Settings

;!Xrange 0s 2.2us

;!AutoUniverse

;!XminRes 1ns

;!YminRes 1n

;!Ok

.STIMULUS C STIM (1, 1);! CLOCK 10MHz 0.5 0 0

+ +0s 0

+ +50ns 1

+ Repeat Forever

+ +50ns 0

+ +50ns 1

+ EndRepeat

.STIMULUS ECR STIM (1, 1)

+ +0s 0

+ 225ns 1

.STIMULUS ECT STIM (1, 1)

+ +0s 0

+ 223ns 1

+ 1.827us 0

.STIMULUS EWR STIM (1, 1)

+ +0s 1

+ 89ns 0

+ 186ns 1

.STIMULUS D1 STIM (1, 1)

+ +0s 0

.STIMULUS D2 STIM (1, 1)

+ +0s 1

.STIMULUS D3 STIM (1, 1)

+ +0s 1

.STIMULUS D4 STIM (1, 1)

+ +0s 0

.STIMULUS R STIM (1, 1)

+ +0s 1

+ 19ns 0

+ 71ns 1

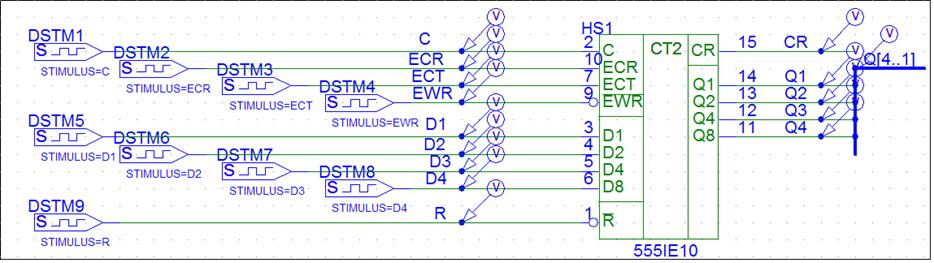

Рис. 3 Схема верификации иерархического символа

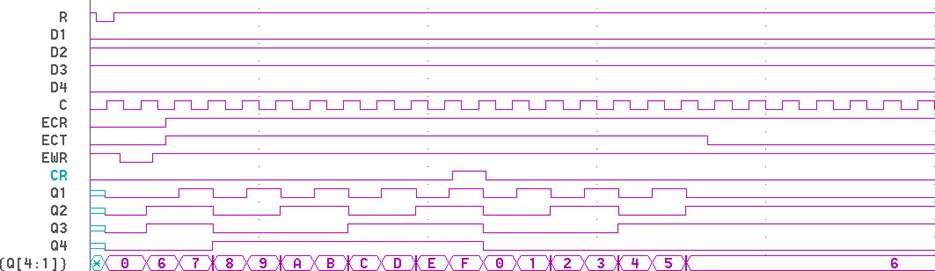

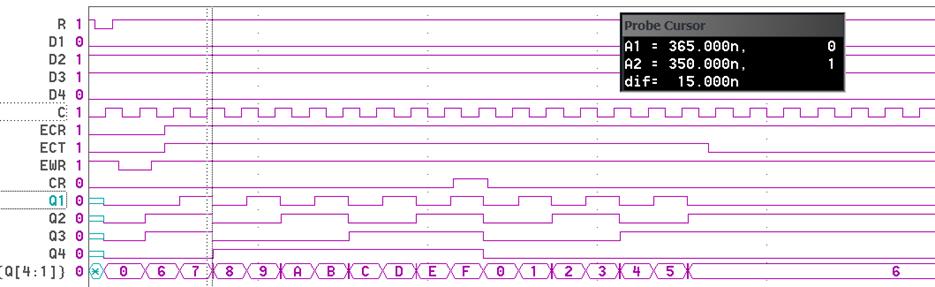

Рис. 4 Проверка правильности работы проектируемого счётчика ИЕ10

Исследовав основные режимы работы проектируемого узла – счётчика ИЕ10 – и убедившись в правильности работы схемы замещения из компонентов по ЕСКД, можно сделать вывод, что данный элемент успешно выполняет нужные функции. Логика его функционирования совпадает с таблицей функционирования счётчика ИЕ10. После успешного прохождения этапа проверки работы проектируемого узла мы переходим к проверке соответствия временных соотношений в схеме замещения.

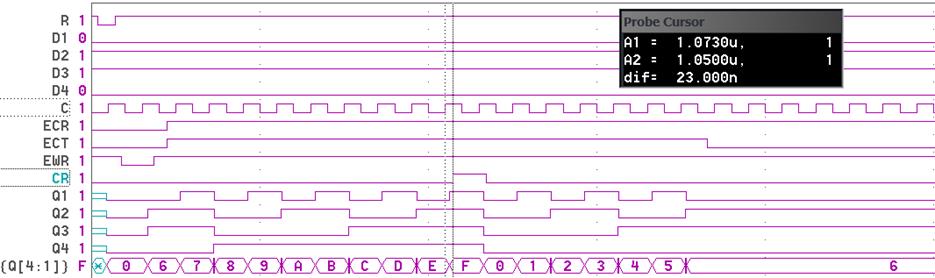

Рис. 5 Время задержки распространения сигнала при включении:

- вход тактирования C – выход переноса CR (0->1) – 23нс;

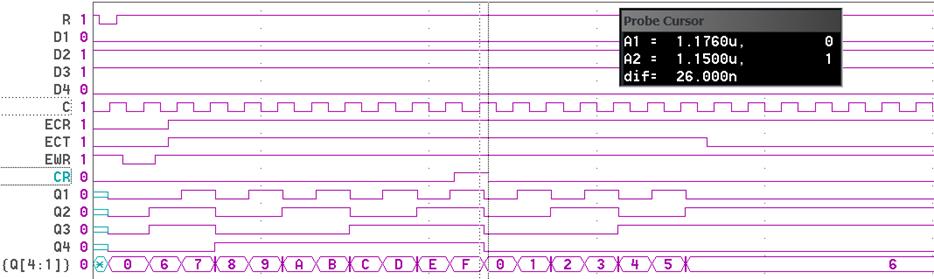

Рис. 6 Время задержки распространения сигнала при выключении:

- вход тактирования C – выход переноса CR (1->0) – 26нс;

Рис. 7 Время задержки распространения сигнала при включении:

- вход тактирования C – выход данных Q8,Q4,Q2,Q1 – 17нс;

Рис. 8 Время задержки распространения сигнала при выключении:

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.