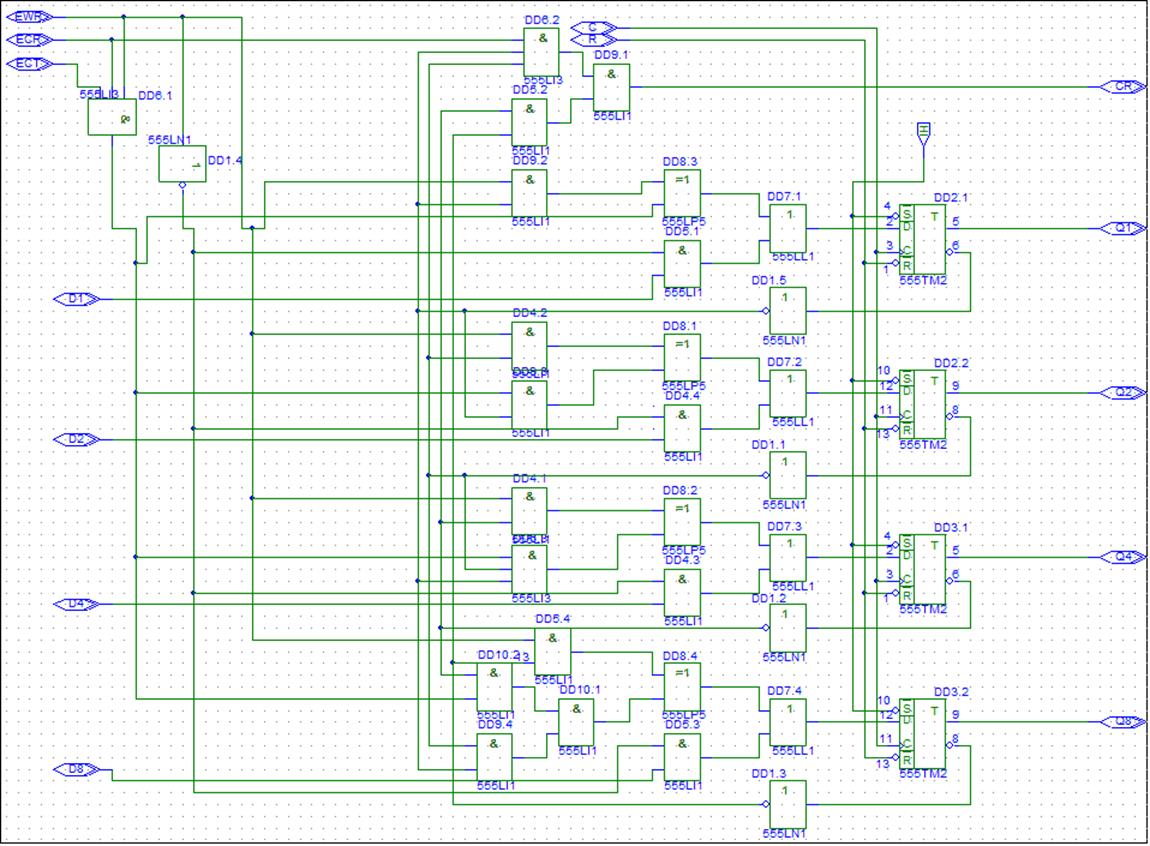

Рис. 2 Схема замещения проектируемо узла

- Путь к моделируемой схеме

* C:\MSim_8\Projects\CourseWork\ctr_schema.sch

- Версия САПР на которой проводилось моделирование

* Schematics Version 8.0 - July 1997

- Дата моделирования

* Fri Sep 23 11:23:17 2005

- Шаг и конечное время моделирования

** Analysis setup **

.tran 20ns 3us

- Путь к файлу с внешними воздействиями

.STMLIB "C:\MSim_8\Projects\CourseWork\ctr_schema.stl"

* From [SCHEMATICS NETLIST] section of msim.ini:

- Подключенные библиотеки

.lib "C:\MSim_8\UserLib\KRLIB.lib"

.lib "nom.lib"

- Файлы со списком элементов цепей

.INC "ctr_schema.net"

.INC "ctr_schema.als"

.probe

.END

* Schematics Netlist *

- Информация о подключенных генераторах внешних воздействий

U_DSTM1 STIM(1,0) $G_DPWR $G_DGND C IO_STM STIMULUS=C

U_DSTM2 STIM(1,0) $G_DPWR $G_DGND ECR IO_STM STIMULUS=ECR

U_DSTM3 STIM(1,0) $G_DPWR $G_DGND ECT IO_STM STIMULUS=ECT

U_DSTM4 STIM(1,0) $G_DPWR $G_DGND EWR IO_STM STIMULUS=EWR

U_DSTM5 STIM(1,0) $G_DPWR $G_DGND D1 IO_STM STIMULUS=D1

U_DSTM6 STIM(1,0) $G_DPWR $G_DGND D2 IO_STM STIMULUS=D2

U_DSTM7 STIM(1,0) $G_DPWR $G_DGND D3 IO_STM STIMULUS=D3

U_DSTM8 STIM(1,0) $G_DPWR $G_DGND D4 IO_STM STIMULUS=D4

U_DSTM9 STIM(1,0) $G_DPWR $G_DGND R IO_STM STIMULUS=R

- Список элементов с входными и выходными цепями, а также название элемента

X_HS1_DD55_1 $N_0001 $N_0002 $G_DPWR $G_DGND 555LN1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD56_2 $N_0003 $N_0004 $G_DPWR $G_DGND 555LN1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD57_3 $N_0005 $N_0006 $G_DPWR $G_DGND 555LN1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD58_1 R $N_0007 C $D_HI Q1 $N_0009 $G_DPWR $G_DGND 555TM2

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD59_2 R $N_0010 C $D_HI Q2 $N_0001 $G_DPWR $G_DGND 555TM2

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD60_1 R $N_0011 C $D_HI Q3 $N_0003 $G_DPWR $G_DGND 555TM2

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD61_2 R $N_0012 C $D_HI Q4 $N_0005 $G_DPWR $G_DGND 555TM2

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD62_1 EWR $N_0004 $N_0013 $G_DPWR $G_DGND 555LI1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD63_2 EWR $N_0002 $N_0014 $G_DPWR $G_DGND 555LI1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD64_3 $N_0015 D3 $N_0016 $G_DPWR $G_DGND 555LI1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD65_4 $N_0015 D2 $N_0017 $G_DPWR $G_DGND 555LI1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD66_1 $N_0015 D1 $N_0018 $G_DPWR $G_DGND 555LI1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD67_2 $N_0004 $N_0006 $N_0019 $G_DPWR $G_DGND 555LI1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD68_1 EWR ECR ECT $N_0020 $G_DPWR $G_DGND 555LI3 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD69_2 ECR $N_0022 $N_0002 $N_0021 $G_DPWR $G_DGND 555LI3 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD70_4 EWR $N_0015 $G_DPWR $G_DGND 555LN1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD71_1 $N_0023 $N_0018 $N_0007 $G_DPWR $G_DGND 555LL1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD72_1 $N_0014 $N_0024 $N_0025 $G_DPWR $G_DGND 555LP5 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD73_2 $N_0025 $N_0017 $N_0010 $G_DPWR $G_DGND 555LL1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD74_2 $N_0013 $N_0026 $N_0027 $G_DPWR $G_DGND 555LP5 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD75_3 $N_0027 $N_0016 $N_0011 $G_DPWR $G_DGND 555LL1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD76_4 $N_0028 $N_0029 $N_0012 $G_DPWR $G_DGND 555LL1 PARAMS:

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.