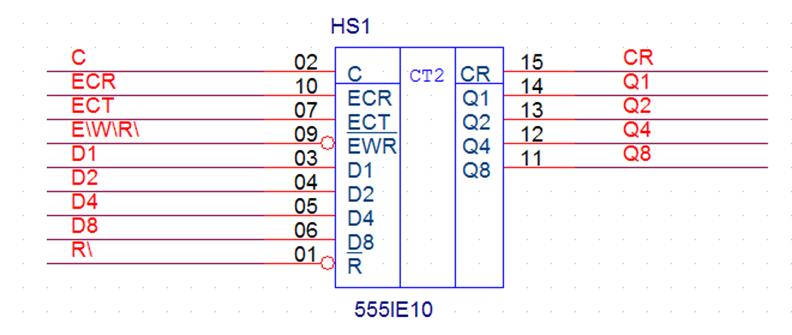

Рис 28 Схема верификации поведенческой VHDL-модели, подключённой к иерархическому символу

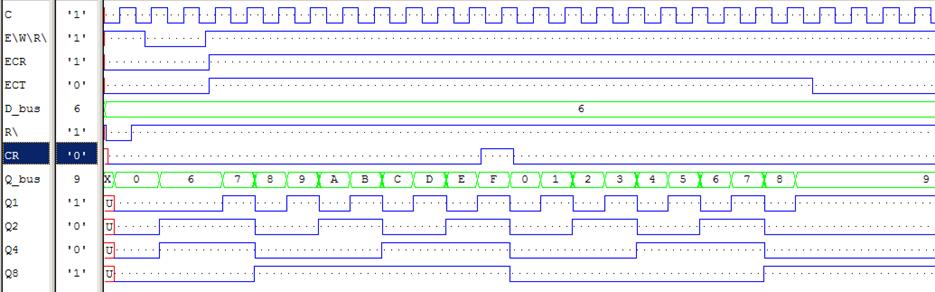

Рис. 29 Проверка правильности работы проектируемого счётчика ИЕ10

Исследовав основные режимы работы проектируемого узла – счётчика ИЕ10 – и убедившись в правильности работы схемы замещения из компонентов по ЕСКД, можно сделать вывод, что данный элемент успешно выполняет нужные функции. Логика его функционирования совпадает с таблицей функционирования счётчика ИЕ10. После успешного прохождения этапа проверки работы проектируемого узла мы переходим к проверке соответствия временных соотношений в схеме замещения.

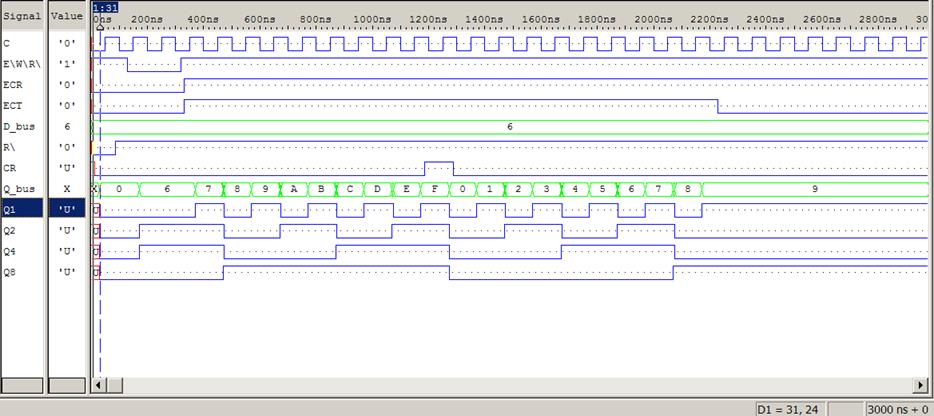

Рис. 30 Задержка

распространения сигнала вход cброса ![]() – выход данных Q8,Q4,Q2,Q1 - 24нс;

– выход данных Q8,Q4,Q2,Q1 - 24нс;

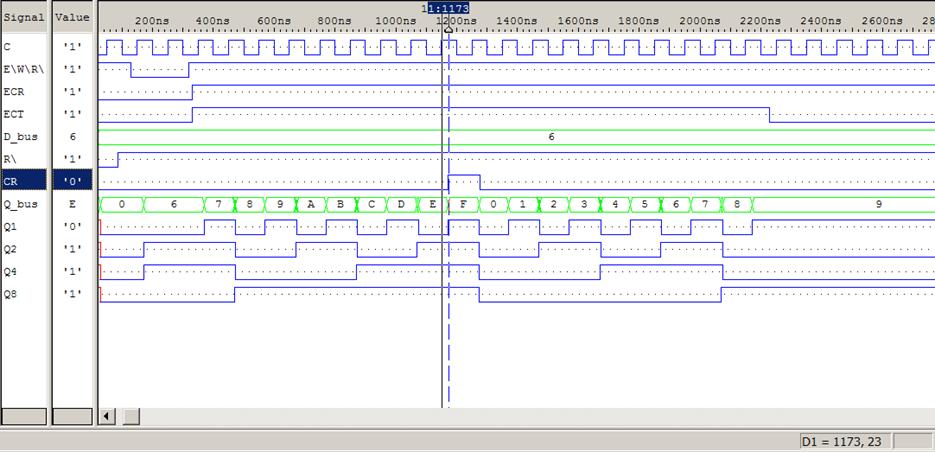

Рис. 31 Время задержки распространения сигнала при включении:

- вход тактирования C – выход переноса CR (0->1) – 23нс;

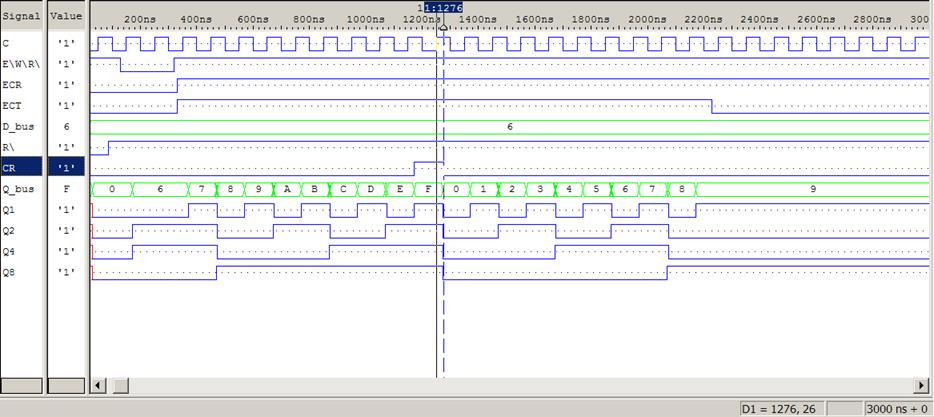

Рис. 32 Время задержки распространения сигнала при выключении:

- вход тактирования C – выход переноса CR (1->0) – 26нс;

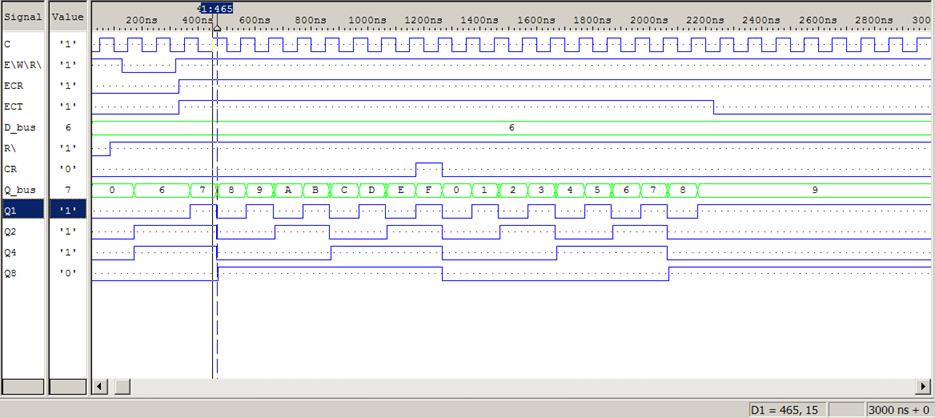

Рис. 33 Время задержки распространения сигнала при выключении:

- вход тактирования C – выход данных Q8,Q4,Q2,Q1 – 15нс;

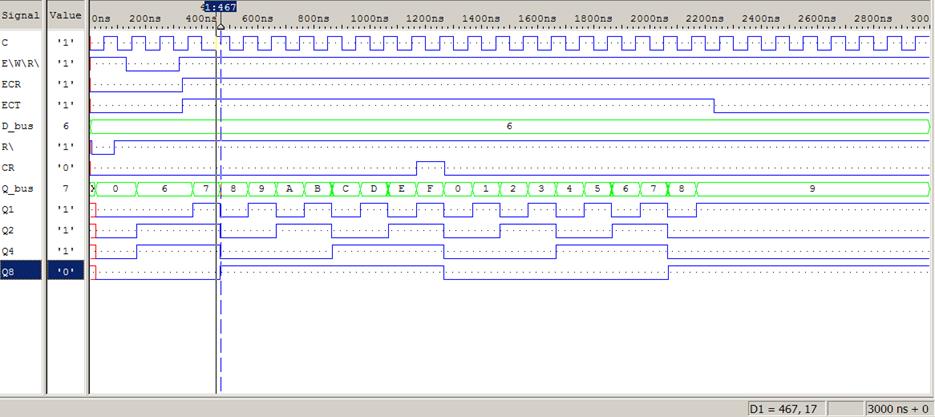

Рис. 34 Время задержки распространения сигнала при включении:

- вход тактирования C – выход данных Q8,Q4,Q2,Q1 – 17нс;

Проделав пункты 19-21, было показано соответствие временных задержек, измеренных при тестировании схемы замещения и VHDL-модели. Как в первом, так и во втором случае они совершенно идентичны.

До изучения пакетов DesignLab 8.0 и OrCAD мною были приобретены навыки проектирования и моделирования цифровой аппаратуры в пакетах Electronic Work Bench 5.12 и MultiSim (EWB 6.0). По сравнению с этими пакетами, и САПР DesignLab 8.0, и САПР OrCAD имеют, на мой взгляд, гораздо более широкие возможности.

Хочется особо выделить следующие возможности пакета DesignLab 8.0 и попутно сравнить с аналогичными возможностями пакета OrCAD 9.1:

· Удобный графический редактор Schematics, удобный пользовательский интерфейс. OrCAD 9.1 имеет также довольно удобный схемный редактор;

· Stimulus Editor – особенно понравившееся мне средство задания внешних воздействий, основными плюсами которого являются простота и наглядность описания сигналов, возможность рисовать курсором эпюры, переключения. К огромному огорчению, пакет OrCAD 9.1 не унаследовал столь удобное средство задания внешних воздействий. Этот факт можно отнести к минусу данного пакета;

· Встроенный текстовый редактор – это уже сложившейся, по моему мнению, непременный спутник любого серьёзного специализированного пакета, определяющий «хороший тон» и адаптированный на решение конкретных задач, имеющий различного рода заготовки, например DSL Template очень помог при написании DSL – моделей. Это безусловный плюс. Пакет OrCAD 9.1 также имеет встроенный текстовый редактор, облегчающий написание VHDL-моделей;

· Постпроцессор моделирования Probe – это ещё один весьма мощный инструмент, позволяющий получить необходимые данные о результатах модельного эксперимента. Очень понравилась возможность легко и просто измерять временные задержки, а также производить различные действия над сигналами, например, объединять их в шину. Пакет OrCAD 9.1 имеет довольно практичные средства визуализации временных диаграмм;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.