+ CLOCK, DELAY(-1,23NS,35NS),

+ DELAY(-1,23NS,35NS)

+ )

+ }

+ FREQ:

+ NODE = C

+ MAXFREQ = 30MEG

+ WIDTH:

+ NODE = C

+ MIN_LO = 25NS

+ MIN_HI = 25NS

+ WIDTH:

+ NODE = NR

+ MIN_LO = 20NS

+ SETUP_HOLD:

+ DATA(4) = D1 D2 D4 D8

+ CLOCK LH = C

+ SETUPTIME = 20NS

+ AFFECTS (4) Q1_O Q2_O Q4_O Q8_O

+ WHEN = { (NEWR!='0 ^ CHANGED(NEWR,0)) & NR!='0 }

+ SETUP_HOLD:

+ DATA(2) = ECT ECR

+ CLOCK LH = C

+ SETUPTIME = 20NS

+ WHEN = { (NEWR!='0 ^ CHANGED(NEWR,0)) & NR!='0 &

+ CHANGED(IEN,20NS) }

+ SETUP_HOLD:

+ DATA(1) = NEWR

+ CLOCK LH = C

+ SETUPTIME = 25NS

+ WHEN = { NR!='0 }

*

.ENDS

*

*$

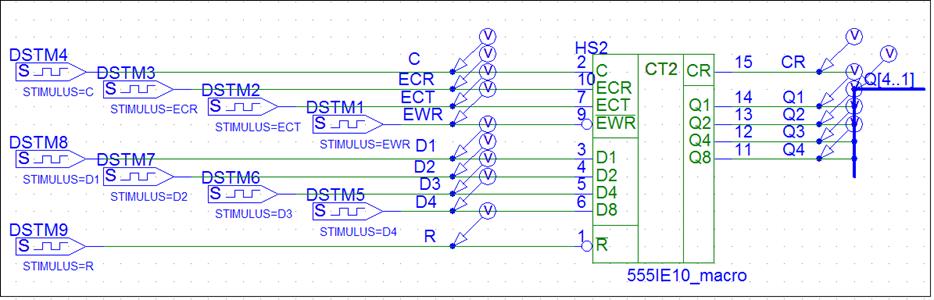

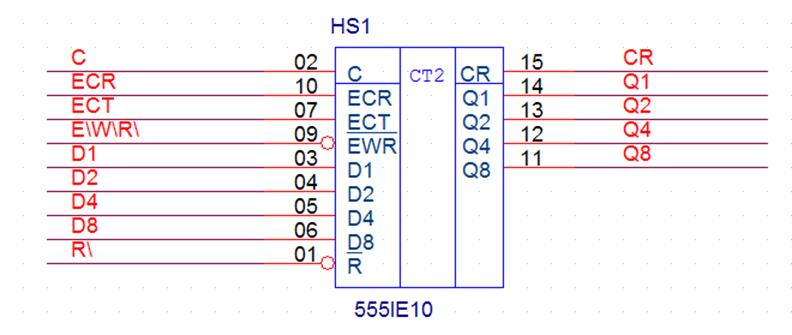

Рис. 12 Схема верификации иерархического символа, поддерживаемого макромоделью

В данном пункте задания требуется особое внимание обратить на идентичность задержек, «заложенных» в макромодель, задержкам, измеренным на схеме замещения узла. Это мы и собираемся сделать:

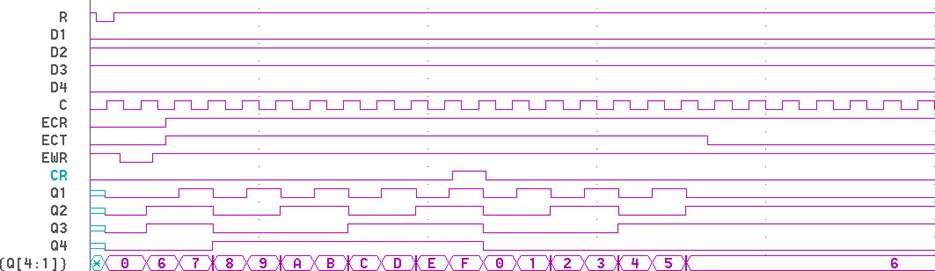

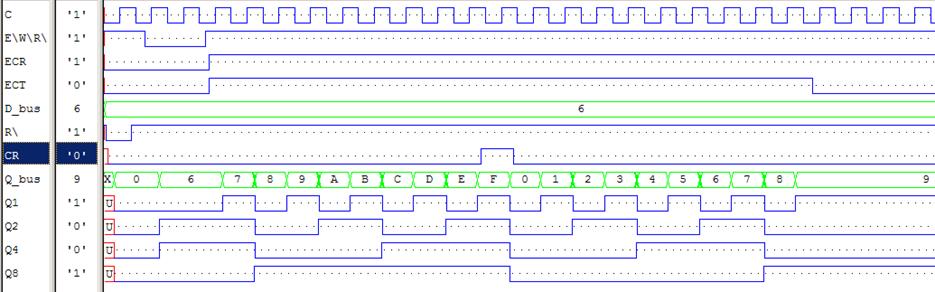

Рис. 13 Проверка правильности работы проектируемого счётчика ИЕ10

Исследовав основные режимы работы проектируемого узла – счётчика ИЕ10 – и убедившись в правильности работы макромодели, можно сделать вывод, что данный элемент успешно выполняет нужные функции. Логика его функционирования совпадает с таблицей функционирования счётчика ИЕ10. После успешного прохождения этапа проверки работы проектируемого узла мы переходим к проверке соответствия временных соотношений макромодели временным соотношениям в схеме замещения.

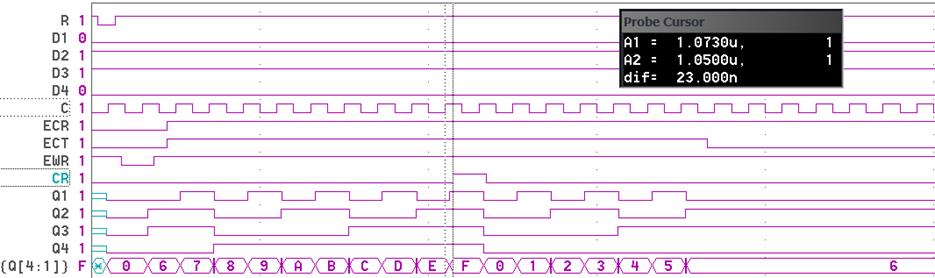

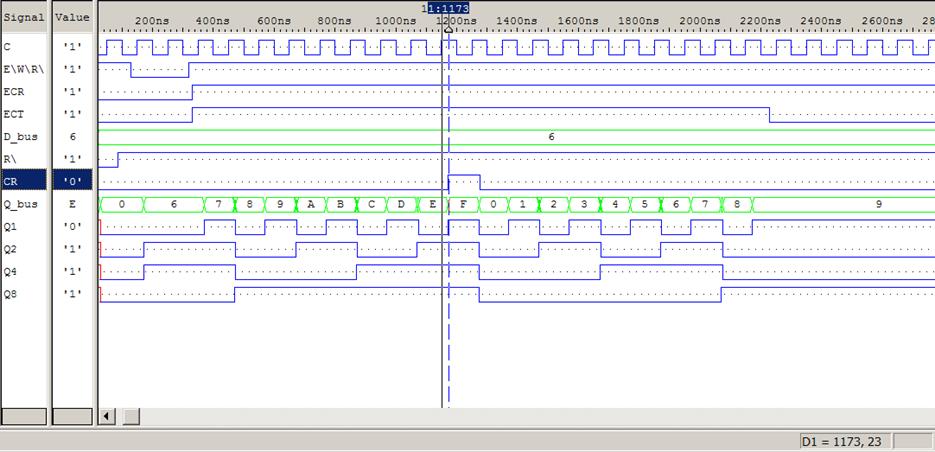

Рис .14 Время задержки распространения сигнала при включении:

- вход тактирования C – выход переноса CR (0->1) – 23нс;

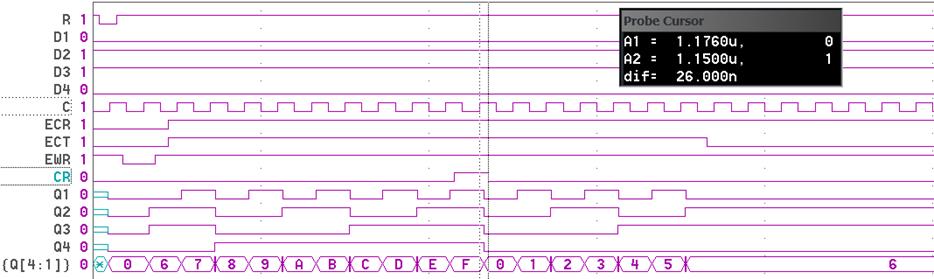

Рис. 15 Время задержки распространения сигнала при выключении:

- вход тактирования C – выход переноса CR (1->0) – 26нс;

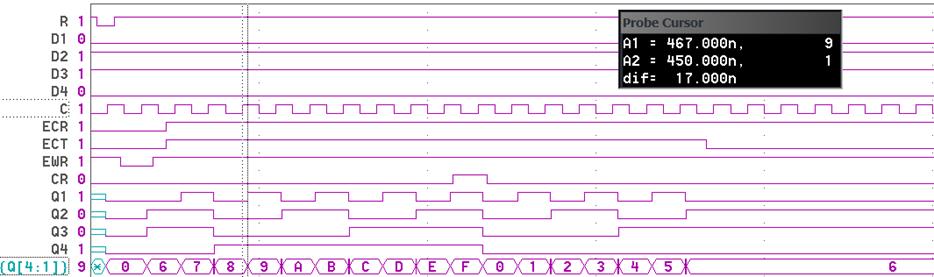

Рис. 16 Время задержки распространения сигнала при включении:

- вход тактирования C – выход данных Q8,Q4,Q2,Q1 – 17нс;

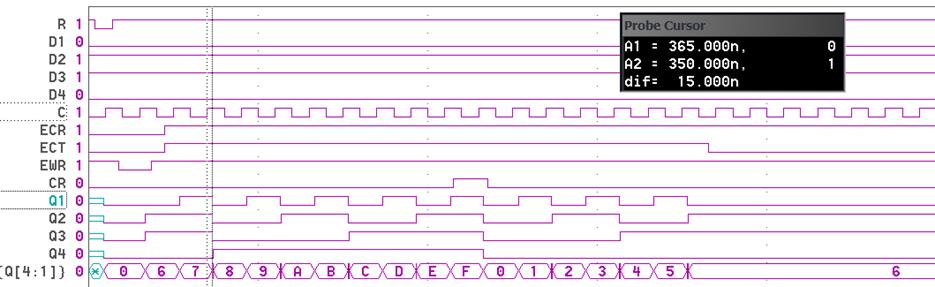

Рис. 17 Время задержки распространения сигнала при выключении:

- вход тактирования C – выход данных Q8,Q4,Q2,Q1 – 15нс;

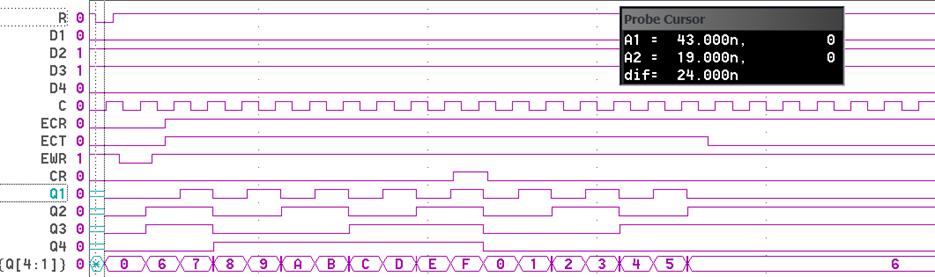

Рис. 18 Задержка

распространения сигнала вход cброса

Рис. 18 Задержка

распространения сигнала вход cброса ![]() – выход данных Q8,Q4,Q2,Q1 - 24нс;

– выход данных Q8,Q4,Q2,Q1 - 24нс;

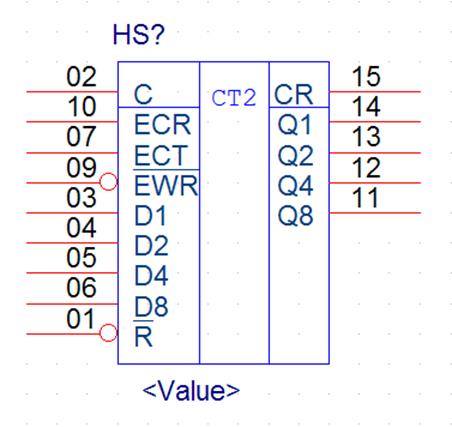

Рис. 19 УГО проектируемого узла (распечатка из графического редактора OrCAD Capture)

Рис. 20 Схема замещения иерархического символа

Рис. 21 Схема верификации иерархического символа

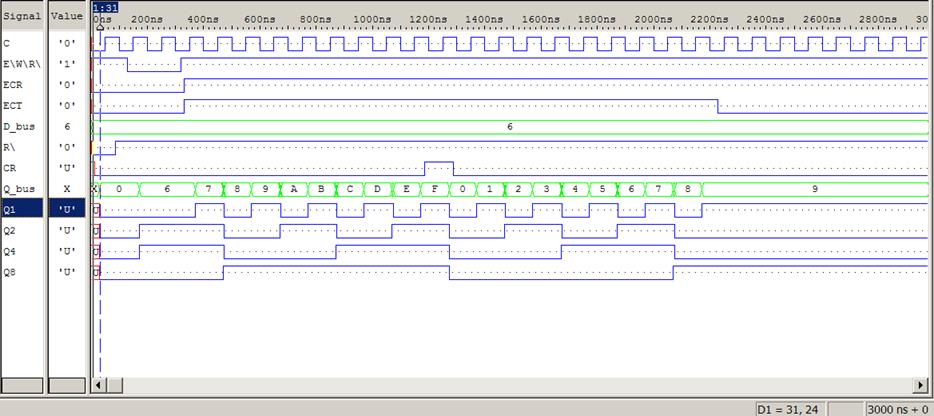

Рис. 22Проверка правильности работы проектируемого счётчика ИЕ10

Исследовав основные режимы работы проектируемого узла – счётчика ИЕ10 – и убедившись в правильности работы схемы замещения из компонентов по ЕСКД, можно сделать вывод, что данный элемент успешно выполняет нужные функции. Логика его функционирования совпадает с таблицей функционирования счётчика ИЕ10. После успешного прохождения этапа проверки работы проектируемого узла мы переходим к проверке соответствия временных соотношений в схеме замещения.

Рис. 23 Задержка

распространения сигнала вход cброса ![]() – выход данных Q8,Q4,Q2,Q1 - 24нс;

– выход данных Q8,Q4,Q2,Q1 - 24нс;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.