Министерство образования и науки Российской Федерации

Новосибирский государственный технический университет

Кафедра вычислительной техники

Курсовая работа

по дисциплине «Моделирование»

Проектирование цифрового узла К555ИР30.

Факультет: АВТ Преподаватель:

Группа: АМ-610 Шалагинов А.В.

Студентка: Королевская В.Е.

Новосибирск, 2010

Содержание

1. Постановка задачи. 2

2. Условное графическое обозначение моделируемого узла. 2

3. Назначение выводов моделируемого узла. 3

4. Режим работы узла. 3

5. Реальные задержки работы узла. 4

6. Описание работы узла. 5

7. Моделирование узла в пакете OrCAD 9.1. 5

7.1. Условное графическое обозначение проектируемого узла в виде иерархического символа. 5

7.2. SPICE – проект. Схема замещения проектируемого узла. 6

7.3. Схема верификации иерархического символа. 10

7.4. Результаты моделировании узла. 11

7.5. Условное графическое обозначение проектируемого узла в виде иерархического символа. 14

7.6. PCB – проект. Схема замещения проектируемого узла. 14

7.7. Схема верификации и результаты моделирования узла 18

7.8. Результаты моделировании узла. 19

7.9. Поведенческая VHDL – модель проектируемого узла. 22

7.10. Схема верификации узла с подключенной VHDL-моделью. 25

7.11. Результаты моделирования VHDL-модели проектируемого узла. 25

8. Моделирование узла в пакете Active-HDL 8.1. 33

8.1. Условное графическое изображение проектируемого узла в виде иерархического символа. 33

8.2. Принципиальная схема замещения узла. 33

8.3. Схема верификации иерархического символа, поддерживаемого схемой замещения. 36

8.4. Результаты моделирования иерархического блока со схемой замещения. 37

8.5. Поведенческая VHDL-модель узла. 41

8.6. Схема верификации иерархического символа с подключенной VHDL-моделью. 41

8.1. Результаты моделирования VHDL-модели узла. 42

9. Выводы.. 46

10. Список литературы.. 47

Общее задание:

Создать структурные и поведенческие модели исследуемого цифрового узла на языке VHDL в пакетах OrCad 9.1, Active-HDL 8.1. Провести имитационные эксперименты с разработанным узлом, целью которых является подтверждение работоспособности узла и проверка на соответствие его временных задержек требуемым. Исследовать возможности используемых инструментальных средств проектирования.

Индивидуальное задание:

Разработать 8-разрядный регистр хранения с адресацией ИР30: зарубежный аналог - 259. Реальный элемент К555ИР30 разрабатывается на элементной базе серии К555: зарубежный аналог – 74LS259, на базе серии 74LS.

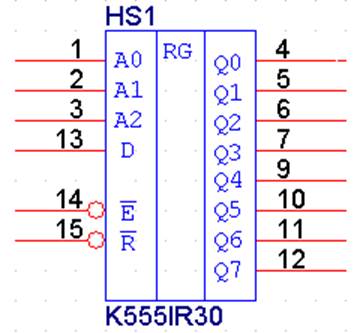

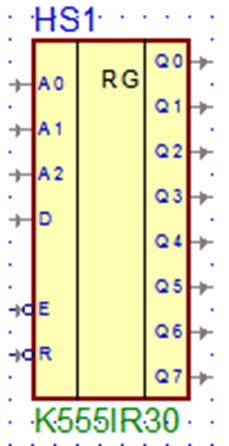

Представим условные графические обозначения (УГО) моделируемого узла в пакетах OrCAD 9.1 (рис. 1) и Active-HDL 8.1 (Рис. 2).

Рис.1. УГО моделируемого узла К555ИР30 в пакете OrCAD 9.1.

Рис.2. УГО моделируемого узла К555ИР30 в пакете Active-HDL 8.1.

8-разрядный регистр хранения с адресацией

Приведем таблицу (табл.1), отражающую назначение выходов моделируемого узла.

Таблица1. Назначение выводов узла К555ИР30.

|

Номер вывода |

Обозначение |

Назначение |

||

|

Входные выводы |

||||

|

1 |

A0 |

Адресный вход |

||

|

2 |

A1 |

Адресный вход |

||

|

3 |

A2 |

Адресный вход |

||

|

13 |

D |

Информационный вход |

||

|

14 |

|

Вход разрешения загрузки |

||

|

15 |

|

Вход установки в "0" |

||

|

Выходные выводы |

||||

|

4 |

Q0 |

Выход нулевого разряда |

||

|

5 |

Q1 |

Выход первого разряда |

||

|

6 |

Q2 |

Выход второго разряда |

||

|

7 |

Q3 |

Выход третьего разряда |

||

|

9 |

Q4 |

Вывод четвертого разряда |

||

|

10 |

Q5 |

Вывод пятого разряда |

||

|

11 |

Q6 |

Вывод шестого разряда |

||

|

12 |

Q7 |

Вывод седьмого разряда |

||

Режим работы узла описан с помощью таблицы (табл.2).

Таблица 2. Логическая таблица режимов работы узла.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.