|

Зарубежный элемент |

Отечественный аналог |

Логическая функция |

|

74LS02 |

К555ЛЕ1 |

2ИЛИ-НЕ |

|

74LS04B |

К555ЛН1 |

НЕ |

|

74LS08 |

К555ЛИ1 |

2И |

|

74LS21А |

К555ЛИ6 |

4И |

|

74LS259 |

К555ИР30 |

8-разрядный регистр хранения с адресацией |

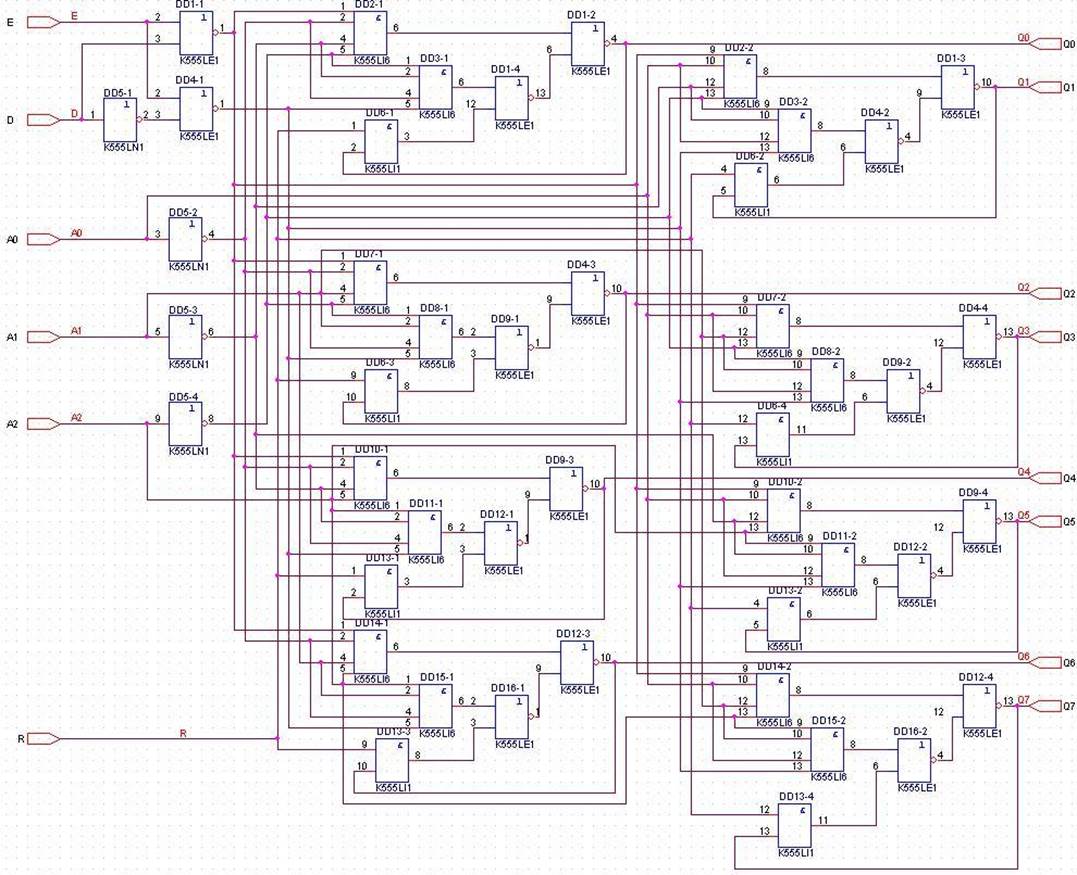

Функциональные описания используемых элементов (листинг 1) были получены из библиотеки зарубежных элементов 74LS.LIB (файл k555.lib). Схема замещения построена на основе используемых в библиотеке «k555.lib» элементов (рис. 5).

Задержки подобраны на основе соответствующей документации [источник 1].

Листинг 1. Функциональное описание используемых элементов.

*---------

* K555LI6 Dual 4-input Positive-And Gates

*

* The ALS/AS Data Book, 1986, TI

* tdn 06/26/89 Update interface and model names

*

.subckt K555LI6 A B C D Y

+ optional: DPWR=$G_DPWR DGND=$G_DGND

+ params: MNTYMXDLY=0 IO_LEVEL=0

U1 and(4) DPWR DGND

+ A B C D Y

+ D_ALS21A IO_ALS00 MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL}

.ends

*

.model D_ALS21A ugate (

+ tplhty=8ns tphlty=8ns

+ tplhmn=0ns tplhmx=0ns

+ tphlmn=0ns tphlmx=0ns

+ )

*---------

* K555LE1 Quadruple 2-input Positive-Nor Gates

*

* The ALS/AS Data Book, 1986, TI

* tdn 06/23/89 Update interface and model names

*

.subckt K555LE1 A B Y

+ optional: DPWR=$G_DPWR DGND=$G_DGND

+ params: MNTYMXDLY=0 IO_LEVEL=0

U1 nor(2) DPWR DGND

+ A B Y

+ D_ALS02 IO_ALS00 MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL}

.ends

*

.model D_ALS02 ugate (

+ tplhty=3ns tphlty=4ns

+ tplhmn=0ns tplhmx=0ns

+ tphlmn=0ns tphlmx=0ns

+ )

*---------

* K555LI1 Quadruple 2-input Positive-And Gates

*

* The ALS/AS Data Book, 1986, TI

* tdn 06/23/89 Update interface and model names

*

.subckt K555LI1 A B Y

+ optional: DPWR=$G_DPWR DGND=$G_DGND

+ params: MNTYMXDLY=0 IO_LEVEL=0

U1 and(2) DPWR DGND

+ A B Y

+ D_ALS08 IO_ALS00 MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL}

.ends

*

.model D_ALS08 ugate (

+ tplhty=0ns tphlty=10ns

+ tplhmn=0ns tplhmx=0ns

+ tphlmn=0ns tphlmx=0ns

+ )

*---------

* K555LN1 Hex Inverters

*

* The ALS/AS Data Book, 1986, TI

* tdn 06/23/89 Update interface and model names

*

.subckt K555LN1 A Y

+ optional: DPWR=$G_DPWR DGND=$G_DGND

+ params: MNTYMXDLY=0 IO_LEVEL=0

U1 inv DPWR DGND

+ A Y

+ D_ALS04B IO_ALS00 MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL}

.ends

*

.model D_ALS04B ugate (

+ tplhmn=0s tplhmx=0ns

+ tphlmn=0ns tphlmx=0ns

+ )

Рис. 5. Схема замещения иерархического символа HS1.

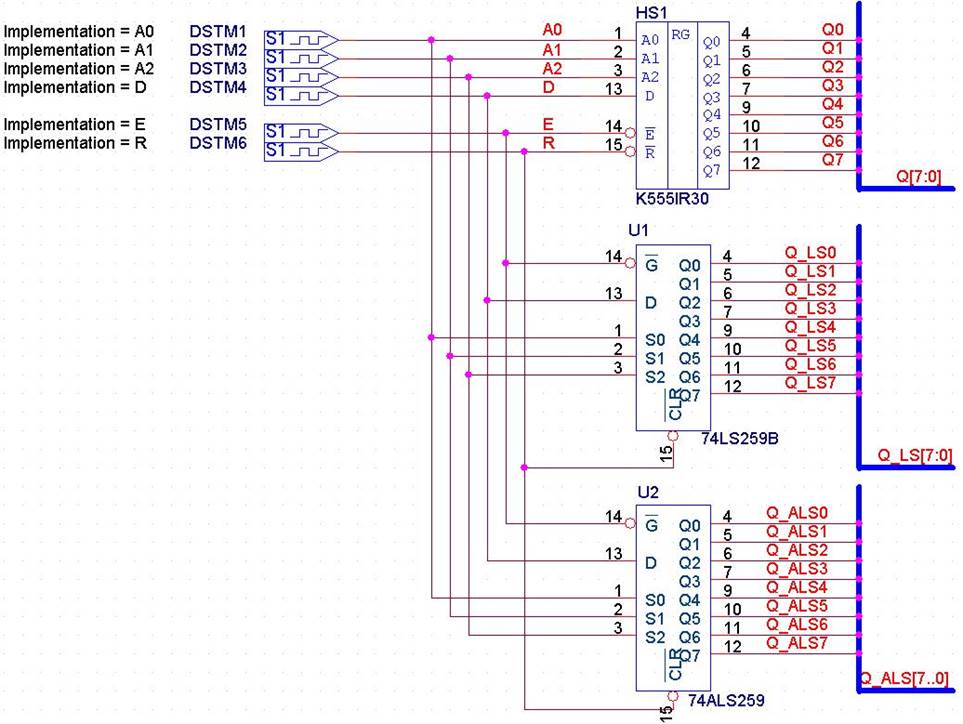

Верификация произведена на основе использования микросхем 259B и 259 серии 74LS и 74ALS соответственно (рис. 6). Данный выбор связан с тем, что микросхеме К555ИР30 соответствует зарубежный аналог 74LS259, которого нет в стандартной библиотеке 74LS. Ни одна из предложенных микросхем не могла быть взята за основу для полной верификации в связи с несоответствием задержек.

По режимам работы микросхем 74LS259B и 74ALS259 убедимся, что созданный элемент функционирует логически верно.

Рис.6. Схема использования микросхемы K555 и зарубежных аналогов 74LS259B и 74ALS259.

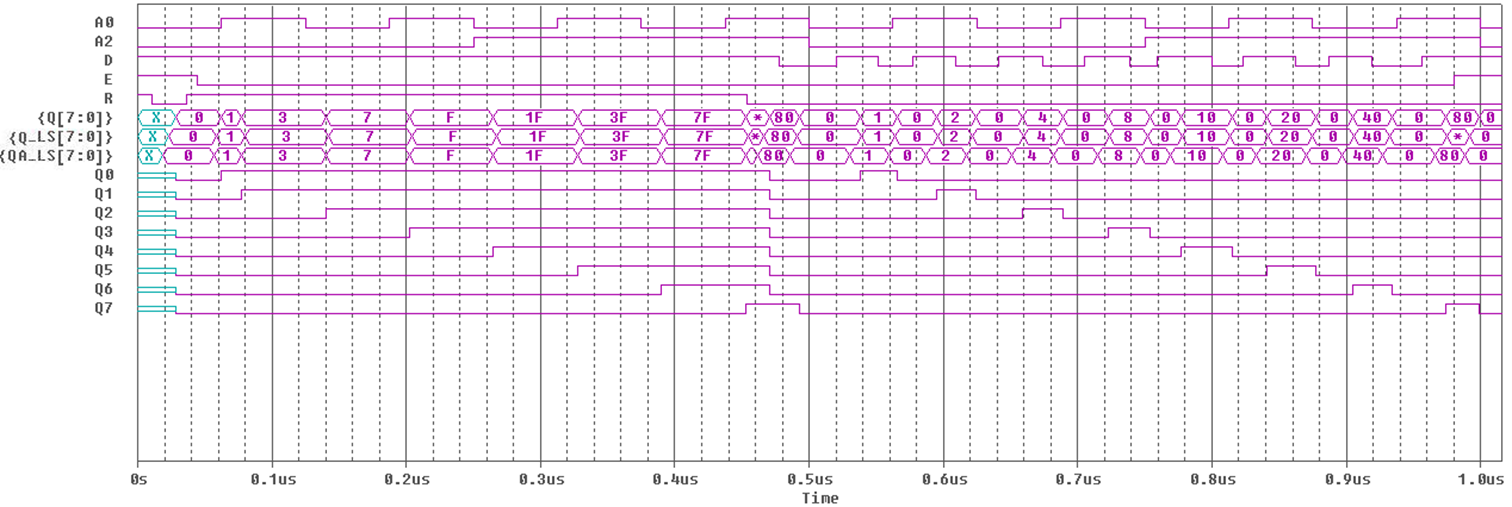

Рис.7. Временная диаграмма работы проектируемого узла

Полученная временная диаграмма отражает все режимы работы проектируемого узла. Выполнив сравнение с зарубежными аналогами, можно сделать вывод, что микросхема функционирует верно. Задержки при распространении сигнала от входов к выходам, отличаются от задержек микросхем 74LS259B и 74ALS259, но совпадают с указанными в необходимой документации [источник 1].

Для того чтобы убедиться в том что задержки подобраны верно, рассмотрены временнее диаграммы моделируемого узла (рис.8-13). Моделирование проводилось для номинальных (typical) задержек.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.