end if;

else -- Режим демультиплексора

if D='0' then

Qt<="00000000" after 15 ns;

else

if (E'event and E='0') then

if A="000" then Qt(0)<='1'after 18 ns;

elsif A="001" then Qt(1)<='1' after 18 ns;

elsif A="010" then Qt(2)<='1' after 18 ns;

elsif A="011" then Qt(3)<='1' after 18 ns;

elsif A="100" then Qt(4)<='1' after 18 ns;

elsif A="101" then Qt(5)<='1' after 18 ns;

elsif A="110" then Qt(6)<='1' after 18 ns;

elsif A="111" then Qt(7)<='1' after 18 ns;

end if;

else

if A="000" then Qt(0)<='1'after 15 ns;

elsif A="001" then Qt(1)<='1' after 15 ns;

elsif A="010" then Qt(2)<='1' after 15 ns;

elsif A="011" then Qt(3)<='1' after 15 ns;

elsif A="100" then Qt(4)<='1' after 15 ns;

elsif A="101" then Qt(5)<='1' after 15 ns;

elsif A="110" then Qt(6)<='1' after 15 ns;

elsif A="111" then Qt(7)<='1' after 15 ns;

end if;

end if;

end if;

end if;

end if;

end process;

Q0<=Qt(0);

Q1<=Qt(1);

Q2<=Qt(2);

Q3<=Qt(3);

Q4<=Qt(4);

Q5<=Qt(5);

Q6<=Qt(6);

Q7<=Qt(7);

end K555IR30_VHDL;

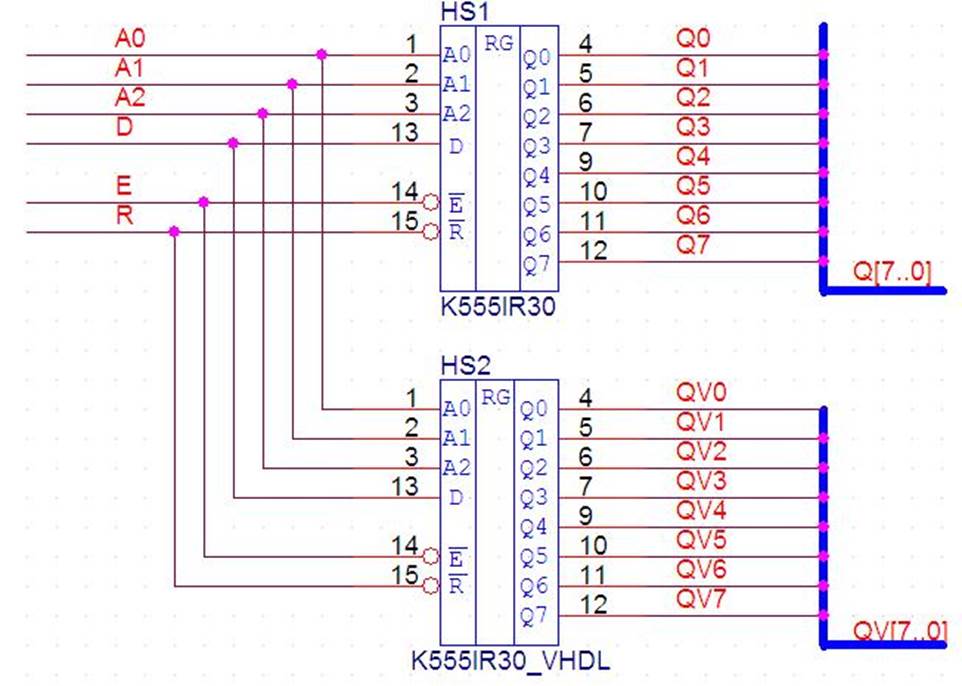

Верификация произведена на основе использования узла, созданного в PCB Simulate – проекте и получившейся в результате проектирования поведенческой VHDL-модели (рис. 24).

Рис.24. Схема верификации элемента со схемой замещения (HS1) с узлом, к которому подключена VHDL-модель (HS2).

Режимы работы элемента в PCB Simulate – проекте полностью соответствуют режимам работы VHDL – модели (рис.25).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.