Условные обозначения:

L – низкий уровень

H – высокий уровень

X – неопределенное состояние

QN – группа выходов

N – номер разряда

QN-1 – состояние, соответствующее предыдущему состоянию

Приведем таблицу (табл. 3) с информацией о задержках для элемента K555ИР30, аналога 74LS259, построенную на основе соответствующей документации [источник 1]. Время предустановки адресов должно составлять не менее17 нс.

Таблица 3. Задержки для элемента K555ИР30

|

Параметр |

От входа |

К выходу |

TYP |

UNIT |

|

tPLH |

|

Q[7..0] |

19 |

ns |

|

tPHL |

18 |

|||

|

tPLH |

D |

Q[7..0] |

18 |

ns |

|

tPHL |

15 |

|||

|

tPLH |

A0, A1, A2 |

Q[7..0] |

15 |

ns |

|

tPHL |

|

Q[7..0] |

17 |

ns |

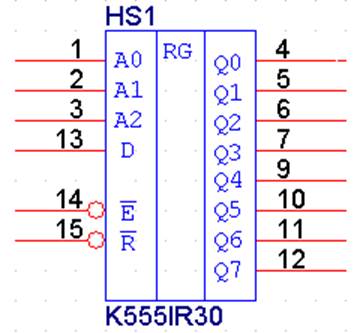

Микросхема К555ИР30 представляет собой 8-разрядный регистр хранения с адресацией. Данный регистр хранения способен выступать в качестве дешифратора трехразрядного двоичного кода и демультиплексора на восемь каналов.

В режиме адресации (режим демультиплексора) данные со входа D записываются в адресуемый триггер регистра и передаются на выход. Остальные триггеры регистра хранят предыдущую информацию. Адрес триггера определяется трехразрядным двоичным кодом, подаваемым не адресные входы А0, А1 и А2 (табл. 4)

Таблица 4. Адресация данных.

|

Входы адресации |

Выход |

||

|

А2 |

А1 |

А0 |

|

|

0 |

0 |

0 |

Q0 |

|

0 |

0 |

1 |

Q1 |

|

0 |

1 |

0 |

Q2 |

|

0 |

1 |

1 |

Q3 |

|

1 |

0 |

0 |

Q4 |

|

1 |

0 |

1 |

Q5 |

|

1 |

1 |

0 |

Q6 |

|

1 |

1 |

1 |

Q7 |

В режиме дешифрации дешифруемый трехразрядный двоичный код

подается на входы А0, А1 и А2. Сигналом истинности будет являться логическая 1,

подаваемая на вход D и сниматься сигнал будет с выхода

триггера соответствующего разряда (предварительно регистр должен быть обнулен).

Режимы работы регистра в зависимости от состояний входов ![]() и

и ![]() удобно

представить в виде таблицы (табл.5)

удобно

представить в виде таблицы (табл.5)

Таблица 5. Режимы работы регистра

|

Входы |

Выход адресуемого триггера |

Состояние выходов неадреcуемых триггеров |

Выполняемая функция |

|

|

|

|

|||

|

L |

L |

D |

L |

Демультиплексор 8 в 1 |

|

L |

H |

L |

L |

Сброс |

|

H |

L |

D |

QN-1 |

Дешифратор |

|

Н |

Н |

QN-1 |

QN-1 |

Хранение |

При изменении напряжения на адресных

входах на инверсном входе разрешения загрузки ![]() должно

удерживаться напряжение логической 1.

должно

удерживаться напряжение логической 1.

Условное графическое изображение проектируемого узла в виде иерархического символа представлено на Рис.3.

Рис.3. УГО моделируемого узла К555ИР30 в виде иерархического символа.

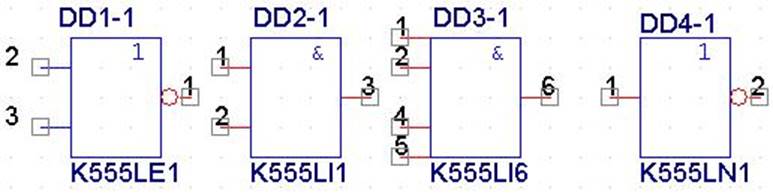

В соответствии с отечественными УГО по ЕСКД создана схема замещения проектируемого узла на базе собственных элементов (Рис. 4). Элементы созданы путем модификации элементов серии 74LS и сохранены в библиотеке k555.olb. Соответствия элементов серии 74LS элементам серии К555 приведены в таблице 6.

Рис.4. УГО символов, спроектированных для реализации схемы замещения цифрового автомата.

Таблица 6. Таблица соответствий отечественных элементов зарубежным аналогам.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.